|

Модули нашего производства УЧПУ видео НЦ-31 успешно работают на станках: 16А20, 16К20, 1В340, РТ755Ф3, 16Б16, 16М30, 4л723ф3 и др. произведенных в СССР с 1980 годов.

16К20Ф3, 16А20Ф3, 16М(К)30Ф3, 1В340Ф3 до 91 г.в. ,1П756ДФ3 , РТ724Ф301 используется УЧПУ НЦ31-16/16.

16К20Ф3, 16А20Ф3, 16М(К)30Ф3, 1В340Ф3 с 91 г.в., 1П756ДФ3, РТ724Ф301 устанавливается УЧПУ НЦ31-48/32

МПУ МС2109 для замены УЧПУ Электроника МС-2109, например на станках 16А20Ф3

СК-1 Сетевой концентратор

Цена: 25 000 руб.

Есть в наличии

Cетевой концентратор СК-1 предназначен для объединения в сеть модулей программного управления НЦ-31 и организует обмен информацией между МПУ НЦ-31, объединенными в промышленную сеть, персональными компьютерами, объединенными в локальную сеть предприятия и устройствами хранения информации (SD картой и сменным модулем памяти (СМП)).

Модуль М16АК20

Цена: 28 000 руб.

Есть в наличии

Модуль М16АК20 предназначен для замены блоков управления (платы электроавтоматики) , установленных на токарных станках с ЧПУ моделей 16К20Т1, 16А20Ф3С39.

Руководство по эксплуатации

Программное обеспечение «Самотестирование Модуль M16AK20

Модуль НЦ ПРЦ

Цена: 22 000 руб.

Есть в наличии

- Заменяет платы ПРЦ, АМТ, ОЗУ 3500

- Позволяет полностью отказаться от дорогостоящих

аккумуляторов - Заменяет устройство ОЗУ-ВП и кассеты внешней памяти

- Позволяет организовать связь с персональным

компьютером

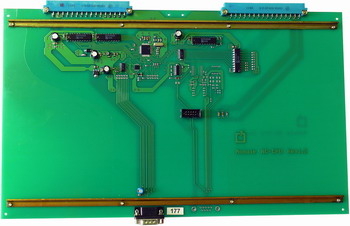

Модуль НЦ ПРЦ

₽22 000

Применяется для ремонта и модернизации УЧПУ НЦ-31. * Заменяет платы ПРЦ, АМТ, ОЗУ 3500, ОЗУ ВП * Позволяет полностью отказаться от дорогостоящих аккумуляторов * Заменяет устройство ОЗУ-ВП и кассеты внешней памяти * Позволяет организовать связь с персональным компьютером

-

Описание

-

Отзывы (0)

Модуль НЦ ПРЦ снимается с производства, рекомендуемая замена Модуль программного управления НЦ 31 Применяется для ремонта и модернизации УЧПУ «Электроника НЦ-31». * Заменяет платы ПРЦ, АМТ, ОЗУ 3500, ОЗУ ВП * Позволяет полностью отказаться от дорогостоящих аккумуляторов * Заменяет устройство ОЗУ-ВП и кассеты внешней памяти * Позволяет организовать связь с персональным компьютером Назначение устройства Модуль НЦ ПРЦ предназначен для замены в УЧПУ НЦ-31 плат ПРЦ, АМТ, ОЗУ 3500, ОЗУ ВП. Модуль НЦ ПРЦ имеет следующие преимущества: * Увеличивается надежность работы УЧПУ и его ремонтопригодность за счет использования современной элементной базы. Значительно снижено энергопотребление по сравнение с оригиналом. * На плате установлена энергонезависимая память, обеспечивающая сохранность параметров, привязок и технологических программ не менее 10 лет без применения аккумуляторов. * Возможен выбор 2, 3, 4 и 4 расширенной версий математического обеспечения. (099,100 234,235 0369,0370 прошивки К596РЕ1). Все версии программого обеспечения записаны в устройство и выбираются пользователм при установке платы. * Возможен выбор различных версий прошивок ППЗУ, ранее установленных на плате АМТ. * Количество рабочих зон памяти увеличивается до 12 за счет использования зон устройства ОЗУ-ВП. * Заменяет устройство 3701 (специальную кассету внешней постоянной памяти) с набором тестовых программ для облегчения ремонта УЧПУ. * Для ввода/вывода в/из УЧПУ технологических программ на плате имеется интерфейс подключения сменных модулей памяти, через которые осуществляется связь с ПК и архивное хранение технологических программ. * Поддерживается возможность записи/считывания всего содержимого ОЗУ (привязки, параметры, программы) для быстрого восстановления работоспособности УЧПУ после программного сбоя.

Севастополь просил критику))

Так вот: ГЕРКОНОВЫЕ КНОПКИ ВАШЕГО КЛОНА (имя которого НЦ-31М) ОСТАВЛЯЮТ ЖЕЛАТЬ ЛУЧШЕГО!!!

Одну из них пришлось перепаивать через пару месяцев. И мелочь, но неприятно, что прозрачные пластиковые крышечки, под которыми находятся картонки с буквами, цифрами и символами со временем начинают выпадать. Кроме того, осталась проблема с залипанием клавиш (особенно весело, когда в ручном режиме при подводе инструмента к детали залипает клавиша быстрого хода!)

Огромное Вам, кстати, спасибо, что парочка кнопок преусмотрительно поставляется в комплекте с СЧПУ)))

И есть встроенная тестовая программа для проверки работоспособности кнопок (главное, чтобы не вылетели те, при нажатии на которые она вызывается).

Очень радует тот факт, что с 04-2008, когда она была установлена, сбоев пока не было (не сравнить с СЧПУ на старой элементной базе)!

И не могу не отметить качество индикаторов, яркость которых РАДУЕТ глаз.

Достаточно часто для модернизации токарных станков используются Модули программного управления НЦ-31-48/32 и МС-2109 с матобеспечением УЧПУ МС-2109, которые позволяют подключаться к электроавтоматике станка без дополнительных контроллеров.

Статья посвящена некоторым вопросам, вызывающим трудности при таких модернизациях и составлена по результатам обсуждений на форуме.

1. Особенности подключения к электроавтоматике станка

Подключение МПУ НЦ-31-48/32 к электроавтоматике станка описано в «Руководстве по эксплуатации» Приложение Г. Подключение МПУ МС-2109 осуществляется по схеме подключения УЧПУ МС-2109.

Наибольшие сложности вызывают подключение переключателей диапазонов частот вращения шпинделя и сигнала контроля зажима резцедержки.

Контроль ступеней частот вращения шпинделя:

Ответ зажима резцедержки:

2. Конфигурация МПУ

Конфигурации МПУ НЦ-31-48/32 и МПУ МС-2109 описаны в соответствующих «Руководствах по эксплуатации» пп. 3.2.

— параметр Х = 5,

— параметр Z — не важен,

— параметр F – зависит от используемого блока питания.

3. Запуск

3.1. Очистить ОЗУ

При включении высветит 241 (испорчен массив параметров)

3.2. Сбросить ошибку

Высветит 7 71 (нет Готовности Станка)

3.3. Включить привода

3.4. Ввести следующие параметры

N7G1 — если не используется пиноль (по умолчанию 0)

N8G1 — если не используется патрон с электрозажимом (по умолчанию 0).

Без этой блокировки и отсутствии сигналов «зажим патрона» и «зажим пиноли» шпиндель не включится.

3.5. Для пробного пуска установить скорости быстрых перемещений в ручных и автоматических режимах 100, после проверки работоспособности установите необходимые скорости.

N2P100

N3P100

N4P100

N5P100

3.6. Масштабирование маховика 1 щелчок — 1 сотка (для маховика 100 имп на оборот и датчика резьбонарезания 1024 имп на оборот)

Ключ в скрытые параметры М6

N5M 17777

3.7. Масштабирование датчика резьбонарезания

N6M31463 – 1024 импульса на оборот

N6M31000 – 1000 импульсов на оборот

4. Известные отличия от НЦ-31

УЧПУ МС-2109 разрабатывалось на основе УЧПУ НЦ-31 с 4-й версии матобеспечения, поэтому с точки зрения программирования и использования они очень похожи. Некоторые отличия есть по параметрам, индицируемым ошибкам. Кардинальное отличие МС-2109 от НЦ-31 – встроенная программа обработки электроавтоматики станка, жестко настроенная на конкретный станок.

Известные отличия следующие:

— МС-2109, в отличие от НЦ-31, не требует ввода диапазона (т.е. в программе прописывать, например, М38 не нужно).

— Можно использовать датчики по осям только 2500 импульсов на оборот.

— Нет возможности настройки времени срабатывания резцедержки. Если не успевает затянуться примерно за 2 с, то появляется ошибка «1» — нет ответа электроавтоматики.

— Привода можно включать только после запуска математики МС-2109.

— Отсутствие сигнала «Толчок шпинделя».

— Отключение контроля патрона и пиноли только через параметры.

— Ключ для просмотра и редактирования параметров – M6, в отличие от М123456 в НЦ-31.

Дополнительные фото:

УСТРОЙСТВО числового ПРОГРАММНОГО УПРАВЛЕНИЯ

«ЭЛЕКТРОНИКА НЦ-31»

Альбом № 4

Ячейка ПРЦ

Техническое описание

3.050.005 ТО

СОДЕРЖАНИЕ

X. Введение.............................. 3

2. Назначение ........................ 4

Технически* данные .................. 4

4. Состав модули ПЯ1.....................7

5. Устройство ж работа процессора........9

5.1. Особенности структуры процесоора.....9

5.Й. Описание блок-схемы..................9

5.3. Описание функциональной схемы.........IX

5.4. Подключение ячейки ПН1 к магистрали

МНН и управление процессором...........20

S.S. Система команд процессора НЦ-31.................................21

5.6. Описание выполнения специфических команд арифметических операций с двойными словами и умножет ня.........29

I. ВВЕЩЬ'ЧИЕ

I.I. Настоящее техническое описанче (ТО) содержит основные сведения, необходимые для изучения процессора (ПН1). входящего в состав УЧПУ "Электроника НЦ-31" в качестве отдельного модуля (3.050.005).

Процессор является основным модулем обработки информации в устройстве чистового программного управления УЧЛУ "Электроника ВД-31" УЧПУ предназначено для выполнения программ управления универсальным токарным станком. Особенности структуры процессора позволяют использовать его в составе технологического, измерительного, контрольно-испытательного оборудования, а также для организации мультипроцессорных систем.

В данном техническом описании приводятся технические характеристики, состав ПРИ и иллюстрация процесса выполнения команд.

1.2. При изучении модуля ПЩ рекомендуется дополнительно руководствоваться схемой электри-’^еской^п^инципиальгой 3.050.005 ЭЗ.(приложение4,

1.3. В настоящем ТО приняты следующие сокращения и обозначения:

- УЧПУ - устройство числового программного управления;

- ПИ! - процессор;

- МВД - унифицированная магистраль семейства микро-ЭВМ ВД;

- М - 16- разрядная внутрипроцессорная

информационная магистраль.

Блоки процессора ОБ - операционный блок;

БЕУ - блок внутреннего управления и синхронизации;

ЕНУ - блок наружного управления;

ИБ - интерфейсный блок;

ПЗУ - постоянное запоминающее устройство.

Функциональные узлы блоков процессора

{АЛЛ - адресный подпропессор

ААУ - адресное арифметическое устройст-

во

УПА - микропрограммная управляющая память адресная

ОШ - операционный подпропессор - ЭАЗ - операционное арифметическое устрой-

СОБ < ш ство У ПО-1, - JBO- 2 - микропрограммная упр'^ляю-. щая память операционная С (два типа кодировки) ЗИИ - микропрог оаммная упрьвдяшая память интерфейсная ПКВД - схема псевдокоманд и векторов преры-' . тдмий ССА - схема опознания (сравнения) адреса СК МВД - схема квитирования по магистрали МВД

СК М - схема квитирования магистрали М СЧЗ РСН - схема чтения/записи содержимого регистров РСН . СПП - схема прерывания процессора ИК - информационный коммутатор

МБ 1 СЗМ - схема захвата магистрали

СК ИБ - схема квитирования интерфейсного блока

„ДМ - схема арбитра магистрали МВД

Регистры процессора:

- АК - аккумулятор БИС АУ

- РСН - регистр общего назначения

- РСЧК - регистр-счетчик команд

- Е5Б 0.1 - регистр базы данных нулевой (первый)

- РУС - регистр-указатель стека

- PC - регистр состояния

- РПР - регистр признаков результата

- РСВ - регистры системные внутренние

- РСН - регистры системные наружные

- РР - регистр режима работы ПЩ

- И - регистр маски ПН!

ВнУтрипроцессорные интерфейсные сигналы: -ЕМ - информация выдана в -агист раль М -ИМ - информация принята по магистрали М - ВА - выдана адресная информация

- ЧТ - чтение по адресу

- ЗА - запись по адресу

- ЧТЫ - чтение модифицированное

- 5М - умножение -Б - блокировка АЛЛ

- ЕБ - предблокировка АПЛ, блок'яи'-вкн ОВД

3

- К - конечная макрокоманда микропрограммы УЛИ

- Т ОБМ- триггер обмена

- Т ВА - триггер фиксации выдачи адреса

• Т СВ - триггер ошибки

«• УСТ - канальная установка и запуск ПШ (рвжям отлвяш)

- НЖ. - регистр макрокоманд БИС АУ (УЛ)

- PIS - регистр ре: има работы № АУ

2. НАЗНАЧИВ®

2.1. Ячейка ПШ в составе УЧПУ "Электроника Щ-ЗГ' предназначена для выполнения:

вычислений адресов данных и команд, размешенных в памяти УЧШ;

- обмена информапией о другими модулями в УЧПУ по магистрали МНЦ;

- обработки операндов:

- микропрограммой и программной частей процедур внешних прерываний;

- микропрограммной и программной частей процедур прерываний по некорректным кедам команд, поступившим на выполнение или по некорректным обращениям извне к процессору.

3, ТЕХНИЧЕСКИЙ "AIiHkE

3.1. Операнды:

- разрядность операндов 16 бит (слово), с возможностью обработки двухсловной и байтовой информации;

- представление чисел - целочисленное, в дополнительном коде, с фиксированной запятой, со знаком в старшем разряде.

3.2. Система команд:

- формат команд - одно и двухсловные (второе слово содержит данные или адрес);

- объем адресуемой памяти команд и данных 64К слов (К=1024);

- способы адресации данных: прямая, непосредственная, косвенная с индексированием;

- способы адресации команд: абсолютная и относительная;

- количество команд, различающихся типом адресации и кодом операции, - 333;

- перечень команд процессора приведен в таблице I.

3.3. Быстродействие выполнения основных операций при работе процессора с памятью, имеющей время выборки,- 1,5 мкс:

- операция сложения типа "регистр-регистр" для: .

16 битных операндов - 90000 оп/с;

32 битных операндов - 35000 оп/с;

- операция пересылки типа "регистр-память" при "короткой" адресации области данных, не менее 25000 оп/с;

- передача управления при "короткой" адресации области программ, не менее 40000 оп/с;

- операции кодового умножения 16 битных операндов 7000 оп/с.

3.4. Регистры:

Состав программно-доступных регистров ПШ приведен в табл.З, из них:

- общее число адресуемых регистров - 23;

- число регистров общего назначения (РОН) -16.

3.5. Система прерываний:

- внешние векторные прерывания - инициатор прерывания передает процессору адрес программ обслуживания;

- внутренние прерывания - сигналы ОШИБКА ОБМЕНА, АВАРИЯ В ИСТОЧНИКЕ ПИТАНИЯ, КОД "НЕСУЩЕСТВУЮЩЕЙ" KOHAHIii переводят процессор ча программы обслуживания, которые начинаются с фиксированных адресов;

- количество приоритетных уровней прерываний -4;

- глубина прерываний - ограничивается объемом памяти, отведенной программистом под стек.

3.6. Состав линий интерфейса модуля ПЩ

Связь с модулями УЧПУ "Электроника НЦ-31" ведется по унифицированной магистрали МНЦ. Состав информационных в сигнальных линий, используемых для подключения ПЩ к магистрали МНЦ, приведен в табл.4.

3.7. Элементная база

В процессоре применены:

- большие интегральные микросхемы KP568BCI -16-- разрядное арифметическое устройство (БИС ДУХ содержащее АЛУ, 16 РОН, схемы управления обменом, внутреннюю схему синхронизации - 2 шт.;

. - большие интегральные микросхемы КН588ВУ1-ОХОХ, KP580EWI-CIO2, КР588ВУ1-ОЮЗ, КР588ВУХ-0Х04, - БИС управляющей памяти (БИС УП) содержат микропрограммы выполнения команд УЧПУ -4 шт;

- большая интегральная схема К596РЕ1 - БИС постоянного запоминающего устройства (БИС ПЗУ), содержит программы управления УЧПУ (постоянную часть), объем 113У-8К слов - 2 шт.;

- микросхемы серии К1601ВП1-22,23,24 - универсальные вычислительные матрицы;

- микросхемы малой и средней степени интеграции ТТЛ - серий KI55, К555, К559, К589, совместимые по уровням электрических сигналов с БИС - 49 шт.

3.8. Номинальное напряжение питания модуля ПШ - +5В + 10 %.

3.9. Потребляемая мощность:

в статическом режиме - не более 5 Вт; в динамическом режиме - не более 8 Вт.

3.10. Система запуска процессора

Пуск ПШ выполняется автоматически от включения питания. При сбое питания производится запись содержимого основных регистров процессора в стековую память с последующим автоматическим возвратом к прерванной программе после восстановления питания модуля.

Таблица I

Система команд процессоре ’Электроника ВЦ-31"

Формат Мнемокод Двоичны! код

СО ,02 Д1 W—и 0 ому iii щ ДДД ДДД

01,03 Д1 И* И 0 (J«L Ш ш ДДД ДДД

04 да QL] (АЛ) РО РО 0 100 МММ . ш ДПД ДПД

05 да Рп] -*&п1 0 101 МММ идд дал ДДД

Об ПУ1 ПУ Д:« <Ы1,УЦ> 0 1Ю МММ МЧД мд ДДД

06 ЛУ’1 ПУ Д:= /ДОС Д> 0 но 001 ОДД ш ДДД

07 РР4 рз — pi 0* III ООО ой iio 333

07 ?РЗ pt -рз—p<i&o),p(ivi) 0 III ООО iii iii 333

II PPI РЗ (АЛ) PI — PI I 001 CH iii iii 333

14 ПМ2 [М1Р] (Ы1) РО I 100 oii оох XX3 333

14 DM2 03 (Ш) рз I 100 0» ООО юз • 333

14 DM2 Chip] сбс> го I 100 let ООХ XX3 333

14 DM2 03 (БС) РЗ I 100 Iii ООО 103 333

14 ПМ1 М — pi I 100 111 iix XX3 333

14 ЙМХ [А ] — PI I 100 III iio 100 ООО

14 J1M2 [MIP] (АЛ) ГО — ГО I 100 KO юх XXJ 333

14 DM2 [А] (АЛ) РЗ —РЗ I 100 »» 100 103 333

15 DMI PI — [MI] I 101 iii iix ХХЭ 337

15 Ш1 PI — 0 J I 101 in iio IDO ОСО

15 DM2 [ШР] (АЛ) ГО — [ИР] I 101 ЯИ ' IOX XX J 333

15 DM2 [А] (АЛ) РЗ —[А] I 10.1 i» 100 103 333

16 DP2 С (HI) РЗ I HO Oct ООО 003 333

16 ПР2 М2Р (Ы1) РО I 110 uii ООО XX3 337

16 ЧР2 С (БС) РЗ I HO let ООО 003 337

16 ПР2 М2Р (БС) ГО I HO let ООО XXI 333 -

16 11Р2 С (АЛ) РЗ — РЗ I 110 CEH 100 003 37J

16 DP2 U2P (АЛ) РО — РО I no И1 100 XX3 773

16 DPI С — PI I HO iii iio ООО ООО

16 DPI М2Р — Pi 1 no iii iio XX7 333

16 PS Р(Э^ 0), Р( 3VI) (АР) РО, PI — po.pi I no ®w он 003 333

16 OCI СРЗ — го I HO . 6oo in 333 333

16 OCI S — СРЗ I no 001 iii 333 333

16 ПУ2 ЕУ(МЗ) :=ПУ РЗ I HO MS* «01 003 773

16 ПУ2 ПУ (М3) :=ИУ А . I 110 iia Й01 010 ООО

16 ПУ2 ЙУ(МЗ) :=НВ I •110 001 101 IIO coo

17 DM3* (УВ) [mi] — Оа] I III МИ oox ХХЭ 333

17 DM3 об) Га]— [а] I III ООО 100 ООО

17 FI (УН) РЗ — РЗ I III io 010 • 003 333

17 P2 (СДВ)РЗ — РЗ I in ш 010 013 733

17 P9 5I6W РЗ — P(jf 0) I III ОН 010 II3 333

17 F3 P(3f 0), P(3V I)

(АР) PO.PI — Р(з( 0), P(3V I) . I III кат on 003 ээз'

17 OCI ГО — СРЗ I in ООО in 333 333

17 OCI СРЗ — <$ I HI 001 III 373 333

17 0C4 СК® I III 100 III IIO 100

17 0C4 ЖДАТЬ I III 101 III IIO 100

• - в формате ВИЗ при адресации к области давних вида [РЗ +А] отсутствует операции +Р (СЛХР) а -Р (БЧПР).

Таблица 2

Таблица кодов операций и адресаций

Мнемокод Обозначение Пояснение

[Щ] XXX [РЗ] ; [+РЗ] ; [А] ; (Ю +А] ;[РЗ -] ; -; -;

М XXX [РЗ) ; [*Р?] ; -; (Pt) ; [РЗ -] ; -;

Адрес шил М2 XX С; РЗ ; *РЗ ; РЗ -;

М2Р XX РЗ ; +РЗ ; РЗ

ыз п РЗ ; А; 5 ;

(Mi) ди;. 'п о 1 «• + Й & ! «»* < & <•» & ••

(УЮ «МЯ -I; О; -Р; +Р; +1; , ; — ♦!; ? ;

UP) юя ПЕР; П—; -; ;

Операция (СЛВ) ИЙ СЛП1; СЫН; САП; СРП; СЛЛ1; ОШ; САМ; СРЛ1;

(БП) S. Л —“Л; П —“ Л; П —• П; Л — П;

(ЕС) S3» ЛЛ; М;

(ПУ) МЖЖ» НПО; IM; БИВ; БП; 1310; ПН1; ИБРА; ШРА; ПРО; DPI; ПБК; ШРК;

ИЗО; 1131; ПЬА; ПМА;

Перечень регистров процессора НЦ-31

Таблица 3

Имя ГРУППЫ регистра Наэсанив регистра Обозначение регистра Разрядность Программный номер регистра Системный номер регистра* Примечание

Регистр Общего назначена» РСН 0 16 00 I7DCOO

Регистр общего назначения Р® I 16 01 170001

Регистр общего назначения ЮН 2 16 02 170002

Регистр общего назначения РОН 3 16 03 170003

Регистр общего назначения РОН 4 16 04 170004

Регистр общего назначения КН 5 16 05 170005

Регистр общего назначения КН 6 16 Об 170006

Регистр общего назначения РСН 7 16 07 170007

Регистр общего назначения РСН 10 16 10 I70010

К® Регистр общего назначения РОН II 16 II I700II

Регистр общего назначения КН 12 16 12 I70012

Регистр общего назначения РСН 13 16 13 170013

Регистр общего назначения РСН 14 16 14 I70014

Регистр общего назначения РОН 15 16 15 I70015

Регистр общего назначения РОН 16 16 16 I70016

Регистр общего назначения РОН 17 16 17 I70017

Регистр базы данных 0 РБД 0 16 20 170020

Регистр базы данных I ВД I 16 21 ITO02I

Регистр указатель стека ГУС 16 22 170022

Регистр счетчик команд РСЧК 16 23 170023

ИР Регистр признаков результата PC 16 40 179040

РСН Регистр режима рр I 63 170063

Регистр Маснв Н1 I 73 170073

Номера регистров приведены в восьмеричном коде.

6 -

Таблы л 4

Перечень линий модуля ПРЦ с магистралью МНЦ

Наименование линии Обозначение XTI ХТ2

Адрес/данные 15 разряд АД <15> А 6

Адрес/данные 14 разряд АД <14? В 6

Адрес/данные 13 разряд АД <13? А 8

Адрес/данные 12 разряд АД <12 > ' В 8

Адрес/данные II разряд АД <11> AI0

Адрес/данные 10 разряд АД <10? BID

Адрес/данные 9 разряд АД <9> AI2

Адрес/данные 8 разряд АД <8> Ы2

Адрес/данные 7 разряд АД <7> BI4

Адрес/данные 6 разряд АД <6> AI6

Адрес/данные 5 разряд АД <5> Ы6

Адрес/данные 4 разряд АД <4> AI8

Адрес/данные 3 разряд АД <3> BI8

Адрес/данные 2 разряд АД <2> А20

Адрес/Данные I разряд АД <1> В20

Адрес/данные 0 разряд АД <0> А22

Признак об ращения к ЬУ ЬУ i Ь *

Синхронизация обмена она А 2

Ответ устройства отв А24

Чтение данных дчт В 2

Запись данных дзп А 4

Пиния передачи управления магистралью

Запрос по прерыванию ЗПР В24

Запрос магистрали ЗМ А22

Разрешение прерывания PLP В26

Разрешение на захват магистрали МНИ (входное) РЭМ и А32

Захват магистрали МНЕ. (выход) РЗМ п В32

Подтверждение запроса ЕТЗ А20

Дополнительные линии

Установка УСТ В 8

Ошибка ведомого ошв взо

Авария сетевого питания ACU BI8

Авария источника питания АЖ AI8 .

Останов ПЯ1 стоп А28

Пуск в шаге ПУСК ш А26

Шины питания

♦5 В А 2, В 2 А32. в32

А 4. В 4 BI2. В20

Корпус All. В22 АЗО, ВЗО

З.Ц. Конструкция

Процессор выполнен в виде конструктивно-функционального законченного модуля. Модуль представляет собой двухстороннюю печатную плату размером 366.7 х 220 мм с размещеннша на ней микросхемами в дискретными электрорадиоэлементами, межсоединения выполнены печатью. Для внешних соединений о другими модулями УЧПУ "Электроника НЦ-31" на плате ПН1 установлено три разъема типа "печать-печать" СНП58-32/94х9В-23-1-В по 32 контакта каждый. Для установки модуля ПШ в корпус УЧПУ имеются флажкоьыа рукоятки.

4. СОСТАВ МОДУЛЯ ПЩ

4.1. В процессор (рнс.1, 2) входят пять основных функциональных блоков, объединенных внутренней магистралью Ы <1б...0> :

- операционный блок - ОБ;

- блок внутреннего управления в синхрошм-UBB - ЕВУ;

- блок наружного управления - ЕНУ;

- интерфейсный блок - ИВ;

- ПЗУ прогреем.

Блоки МБ в ЕНУ подключены к магистрали МВЦ <15...0> .

Рис. I. Блок-схема процессора "КЦ-31”

I -магистраль ЬВД (I5...0); И - управление обменом с регистрами СБ; П - управление обменом;

1 У - синхронизация обработки внешних обращений;

У - прерывание ПН(; У1 - синхронизация С5; VI -магистраль М (15...О); УШ - узел запуска ПЩ

п

Ю

М~-^НЦ

БВУ

УПИ

Г"О"

ПЗУ

Рис. 2. Блок-схема ПЗУ процессора:

I - схема управления; U - схема опознания адреса; Ш - накрпитвль информации

4.2. Конструктивно устройство ПЗУ расположено на плате 035 3500 (3.069.344) и соединяется с модулем процессора кабелем 4.853.071 по третьему разъему. ИЗУ хранит постоянную часть программ работа „ЧПУ “Электроника (область памя-

ти программ, объем адресуемой памяти R К слов, адресное пространство 0...317777g). ЬЗУ состоит из накопителя, собранного на микросхемах Х5Э6 FEI, и узла управления, обеспечивающего интерфейс обмена по внутренней магистрали М ПН*. Блок-схема устройства L35 приведена на рис.2.

Распределение микросхем по блокам ПИ*: ОБ - D I...D3.3 5... 3 8, 3 28.. D3C, D38 , 3 39.

342. .. D45, D48. D49, С53, D54, D57; БВУ - П4, 0 7, 3 8, Dl4, PI5, 1)17, 3 22, Р23, У28, J>34,1)36, 341, 343,344,348, D5I, «52, D&4, -D58,’

БНУ - D8 ... 314. 316... 319, 321...В 23, D28. 333... D37, 340, 346 ... 348, D50. v55; ИБ - D7, 38, 314, 315. 320, 322, 324...» 27, D3I, u32.

Таблица 5

Распределение типов ИМС В модуле ЕН1 (шт.)

Серия К555 Серия К155 Серия К559

JKI - 3 ЛАЗ-2 ДА4 - I М9 - I ЛЮ - 6 лнз - 4 ДИ - 1 ЛН2 - 7 ТМ2 - 2 КГЗ - 5 ЛЕ1 - I i яр О я §

Серия К588

Ю1 0101 I ЬУ1 0102 I Ы 0103 I ВУ1 0104 I BCI 2

Серая К1801ВП

Серия №61 022-1 023 - I 024 - I

КГЗ - I

Серия К589

АП26 - 4

5. УСТРОЙСТВО И РАБОТА ПРОЦЕССОРА

5.1. Особенности структуры процессора

Основными особенностями структуры модуля ПН! является:

- организация совмешения и распараллеливания выполнения операций;

- микропрограммная организация вычислительного процесса;

- асинхронный принцип передачи информации по магистралям и взаимодействия блоков;

- построение мультипроцессорных конфигураций УЧПУ;

- возможность диагностики работы модуля.

Принцип распараллеливания и совмещения оперений реализован включением в состав процессора двух арифметических подпроцессоров - адресного и операционного - выполняющих определенные действия по команде одновременно. Операционный подпроцессов производит обработку операндов, адресный -готовит значения адресов операндов, команд и результатов. В частности, предусмотрено совмещение выполнения текущей команды с выборкой следующей команды из памяти УЧПУ.

Принцип микропрограммного управления является особенностью типового набора БИС серии К588 и реализуется с помощью применения в процессоре микропрограммной упцт.тхмоей памяти, построенной на БИС УП. Макрокоманда, поступающая из памяти УЧПУ, инициирует различные микропрограммы одновременно в управляющей памяти операционного и адресного подпроиессоров. Содержимое управляющей памяти этих подпроцессоров различно и для ее реализации применено три типа БИС УП.

Асинхронная передача информации по внутренней магистрали М ПШ организуется с помощью специальных линий "Информация выдана" (ЬМ), "Информация принята” (ИМ). Источник информации возбуждает вместе с выдачей информации сигнал на линии ВЫ. Приемник информации после приема возбужает сигнал на линии ПМ. Только после этого источник снимает возбуждение сигнала с информационных шин и линии ВМ, а приемник - с линии 1Ш. В канале микропрограммного управления принцип асинхронного взаимодействия выполняется введением в канал упдоляощмх линий "Начать” (Н) и "Исполнено" (41), определяющих начало и окончание микрооперации в подпропессорах. Асинхронная работа адресного и операционного подпропессоров и различная длительность выполнения команд в каждом из них требует синхронизации подпроиессоров. Синхронизация осуществляется анализом совпадения сигналов окончания микропрограмм в каждом подпропессоре и обеспечивает одновременность перехода блоков ПН! к выполнению следующей команды. Кроме того, при обменах ПН! с другими модулями УЧПУ, ввиду неопределенного времени занятости магистрали МНЦ в многопроцессорном УЧПУ, введена внутренняя подсинхронизация операционного блока. Внутренняя под-синхронизация СБ предотвращает конфликтные ситуации обмена подпроцессоров по магистрали М.

Требования построения мультипроцессорных конфигураций УЧПУ и возможность проведения диагностики работы БИ! удовлетворены введением в состав процессора блока наружного управления, БНУ обеспечивает адресное обращение к процессору по магистрали МВД по чтению/записи его программно-доступных регистров.

5.2. Описание блок-схемы

5.2.1. Операционный, блок (ОБ)

ОБ предназначен для вычисления адресов команд. и операндов, выполнения арифметико-логических действий над операндами.

ОБ включает в себя (рис.1):

- 16-разрядяое арифметическое устройство адресное - ААУ;

- 16-разрядное арифметическое устройство операционное - ОДУ;

- микропрограммную управляющую память адресную - УПА;

- микропрограммную управляющую память операционную - УПО1, УП02;

- узел управления - Л.

Структурно СБ представляет собой четырехмагистральный блок. Первой магистралью является внутренняя магистраль процессорам (I5...0). К магистрали М подключены 16-разрядные информационные каналы адресного арифметического устройства ААУ, операционного арифметического устройства ОАУ и 16-разрядные входы регистров команд УПА, УПО1, УПО2. Выходы регистра микрокоманд РЫК УГ.А и входы FMK ААУ образуют вторую магистраль. Выходы tWK УПО1 и РлК 5ПО2 объединены по схеме логического "ИЛИ" и соединены с входом ШК ОАУ. Данное соединение представляет третью магистраль СБ. Для организации ветвления в командах условных переходов по признакам результата выполнения команд (расширение - Р, знак - 3, переполнение -II, нуль - И) в состав ОБ введена четвертая магистраль. Она связывает выходы 4-разрядных регистров состояния PC ААУ и ГС ОАУ с входами регистров состояния ГС УПА в ГС УП02.

При выполнении операций над 16-разрядными операндами арифметические устройства ААУ и ОАУ исполняют автономно адресную и операционную части микропрограммы выполнения команды. Для выполнения действий над 32-разрядными операндами и для команды умножения осуществляется микропрограммное перестроение ААУ и ОАУ в единый 32-разрядный блок.

Узел управления У1 используется для внутренней синхронизации обмена информации между узлами ОБ

5.2.2. Блок внутреннего управления (Б1У)

БЬУ предназначен для:

- управления обменами по внутренней магистрали М (15...О) ПЩ;

- управления интерфейсным блоком при обменах между магистралями МВД (15...0) и М ( 5...0), возбуждаемых процессором;

- участия, наряду с БНУ, в управлений <бме-нами по МНЦ, инициируемый другими активными х*>-

- 9 -

далями УЧПУ по чтению/запвси группы РСВ регистров г. раде ссора;

- управления выполнен!эм проц*чгур прерывания в ПЩ.

БВУ состоит ж8 следующих узлов (рис Л):

- мигрспрограхляой управляющей памяти внут-рипроцессорного интерфейса (УЛИ);

- схемы формирования кодов псевдокоманд и векторов прерываний (ЦКВП);

- сх«и упгавленд СУ2.

К магистралям М (15...0) подключены:

- 16-разрядяый вход регистра команд FK УПИ, для приема кодов команд, поступивших на выполнение;

- 6—разрядный выход схемы ПКБП, для трансляции в магистраль значащих разрядов псевдокимавд и фиксированных векторов прерываний.

5.2.3. Блок наружного управления (БНУ)

ЕНУ предназначен для управления:

- обменами при обращениях к UMI по системным адресам его регистров на МВД;

- сменой режима работы процессора;

- структурными элементами ОШ при выполнении процедур прерываний;

- формированием признаков внешних прерываний.

В состав БШ входят схемы:

Распределение

- опознания адреса процессора (ССА);

- формирования сигналов квитирования обмена информации по магистрали МВД (СК МВД);

- форм» .5иия сигналов квитирования обмена мнфодаацди но магистрали М (СКМ);

- регистров РСН ПЩ с упрцвляавей логикой обмена информации по магистралям М и МНЦ (РСН);

- обращения к регистрам системным внутренним (РСВ);

- формирования признаков прерываний ПЩ по аварии в источнике питания или при ошибке обмена с магистралью МВД (СПИ).

Основные структурные связи БНУ

К линиям адреса~данных АД МВД подключены:

- 12-разрядный вход схемы ССА, для приема кода адресного обращения к ШЩ;

- первый 6-разрядный выход схемы СЧЗ РОН, для трансляции в магистраль МВД текущего значения регистров РСН и собственного адреса процессора.

К магистрали М подключены:

- 6-разрядный выход схемы ССА для передачи в магистраль адреаа регистра ПН1 (группа РСВ) при чтеиви/записи последнего по МВД;

- второй 6-разряцный выход схемы СЧЗ РСН для трансляции в магистраль текущего значения регистров РСН в собственного адреса процессора.

5.2.4. Интерфейсный блок (ИБ'

Таблица 6

регистров ОАУ и ААУ

ОАУ ш

Регистр Еоясиекие Регистр Полевение

HJ РОН 0 РО й

П ЮН I ‘ И Множитель (ЛвО)

ГС РСН 2 Р2 &

РЗ РСН 3 РЗ Вспомогательный регистр

Р4 РОН 4 14 и

F5 РОН 5 Р5 (100000)

Р6 РСН 6 Р6 к

ГС РСН 7 Р7 (17777)

РТО РСп 10 РЮ X

PII РСН II PII шо

PI2 РСН 12 И2 а

ИЗ РСН 13 PI3 ИЛИ

И4 РОН 14 Н4 а

И5 РСН 15 PI5 ж

И6 РСН 16 PI6 и

PI7 РОН 17 PI7 РСЧК

АК АККУМУЛЯТОР АА АККУМУЛЯТОР

ГС И1Р ГС РЕГИСТР СОСТОЯНИЙ

и - микропрограммы* "чепнпе" регистры, используемые при выполнении команды УМНС.

ЛЬ ,редказиачзн для:

- ; погядоч штиля последовательности обменов между устройствами по магистрали МВД;

- информационной связи процессора с другими модулями УЧПУ.

. В состав блока входят:

- схема арбитра магистрали МВД (AM);

- схема захвата магистрали (СЗМ);

- схема информационного коьедутатора обмена ЕИ1 с МВД (ИК);

10 -

Рис. 3. йункцианальная схема ОБ:

I - магистраль М <15... 0> ; Ц - узел ФТ УПА;

Ш - узел перестройки формата слова ОБ; 1У - узел

О PC; У - демультиплексор микрокоманды; У1 - узел

К ААУ; УБ - узел Н ОАУ и блокировки ОПП, У1В - управляющие сигналы БЫ; IX - узел блокировки А1Ш;

X - усилители команды j XI - узел Ф1 УНО

- схема формирования сигналов управления и сигналов-идентификаторов обмена интерфейсного блока с магистралью МЩ (СК ИБ).

5.3. Описание функциональной схемы

5.3.1. Адресный подпродессор (АЛЛ)

На функциональной схеме операционного блока (рис.З) представлен адресный подпроцессор, состоящий из:

- адресного арифметического устройства;

- микропрограммной управляющей памяти адресной;

- схем синхронизации работы АПЛ в составе СБ.

Адресный подпроцессор предназначен для выполнения процедур формирования физических адресов (С4А) операндов, команд и результатов.

5.3.1.1. Арифметическое устройство АПЛ выполнено на одной БИС АУ серии К5В8 (K588BCI). Структурная схема БИС арифметического устройства (АУ) представлена на рис.4. В состав БИС АУ входят следующие функциональные блоки:

- параллельное арифметико-логическое устройство (АЛУ);

- блок регистров общего назначения ГО...Р17;

- регистр состояний (PC);

- рабочий регистр (аккумулятор АК);

- регистр микрокоманд (РЫК);

- регистр режима (РЮ;

- блок расширения (БР);

- буферный регистр магистрали данных со схемой (МД);

- буферный регистр магистрали состояний (ИС);

- блок управления (БУ);

- блок синхронизации (БС).

Рассмотрим назначение блоков БИС АУ по рис. 4.

АЛУ - предназначено для выполнения арифметико-логических операций над 16-разрядными операндами (словами) или над старшими байтами слов, поступаххдки по шинам А и В. В состав АЛУ хводят: коммутатор, сушптор с цепями переноса и сдвига, блок записи в обмена байтами, регистр предварительного хранения.

Блок РОН предназначен для оперативного хранения данных в БИС АУ. Блок РСН включает 16 шестнадцатиразрядных регистров, доступных по чтению или записи. Распределение регистров ААУ пря-ведеио в табл.6.

PC - имеет 16 разрядов, 6 старших индицируют состояние АЛУ. Признаки результата операции фиксируются в 4-х старших разрядах PC на триггерах:

_ wp« _ "расшлрелие", триггер принимает значение переноса из данного БИС АУ в следующий в арифметических операциях или значение выдвигаемого бита в операциях сдвига, в логических опер?' и

«1

ях (ИЛИ, И, НЕ) и в пересылках, принимает значение "0я;

- "3" - знак, принимает значение старшего разряда результат.

Рис. 4. Структурная схема БИС АУ:

I - регистр режима; 11 - буферный регистр состояния; IK - регистр состояния; 1У - блок записи и обмена байтов; У - регистр предварительного хранения; У1 ~ комбинационная часть, коммутатор;

УЗ? - рабочий регистр (аккумулятор); УШ - блок РСЙ (16x16); IX - буферный регистр магистрали данных;

X - магистраль данных; XI - магистраль микрокоманды; XII - регистр микрокоманд (ШК); ХШ - блок управления (БУ); Х1У - схема обмена; ХУ - блок расширения (ЬР);. ХУ1 - блок синхронизации (БС); ДБ -блок АЛУ

-"П" - ’’переполнение*', отражает переполнение разрядной сетки в арифметических операциях, в других операциях значение ”П" не меняется;

- "Н" - "ноль", принимает значение "Iя, если результат операции равен нулю по всем разрядам.

АК - предназначен для временного хранения 16- разрядного операнда. Адрес АК задается неявно, форматом макрокоманды.

ИДК - используется для записи и хранения 12-разрядного кода микрокоманды, поступавшей в БИС ДУ.

РЫ - 3-разрндный регистр, содержимое которого определяет режим функционирования БИС АУ ("старший", "младший").

БР - согласует цепи переноса и сдвига (СО, CO, CI6, CI6) БИС АУ гри расширении разрядности ОБ.

Мд - выполняет асинхронный прием/выдачу информации по 16-разрядной магистрали данных (KI).

МС - предназначен для выдачи и временного хранения любого полубайта К' в РгЖ.

БУ - дешифрует коды микрокоманд и формирует упрналяюсде сигналы. Стробируется сигналами вз БС.

БС - формирователь внутренних синхросигналов, обеспечивавших выбранный режим работы БИС АУ. Формирует также внешние синхросигналы для совместной работы нескольких БИС АУ либо связки БИС АУ БИС УН.

В операционном блоке канал KI ААУ подключен к магистрали М для исходной загрузки служебных регистров (см.табл.3) для информационного обмена содержимым любого регистра с магистралью М и для выдачи сформированных в ААУ адресов операндов в команд. Приемником этих адресов является информационный коммутатор ИБ.

Регистры Р5 и Р? ААУ хранят начальные const, загружаемые в процедуре ИНАЯ для дальнейшего использования в некоторых видах адресаций. Регистры четные используются как "черные" микропрох'рам-мные рег«стры при выполнении команды умножения. ААУ связанс с микропрограммной управлявшей памятью УНА 13-разрядноЙ магистралью, ;де 12 разрядов представляют поле микрокоманды, а 13-й резряд "начать” (Н - принять и выполнить микрокоманду) синхронизирует прием микрокоманды на FMK БИС АУ.

.. 5.3.1.2. Микропрограммная управляющая память АПЛ выполнена также на одном БИС серии К588 (К588ВУ1). Структурная схема БИС УП представлена на рис.5. БИС УП содержит:

- постоянную память типа "программируемая логическая матрица" (ШМ);

- программируемый слой инверторов;

- входные регистры РК (PI < 0...I5 ) и ГС (Р2 < О...3> );

- два регистра обратной связи: регистр следующего адреса (ГСА < О...6>) и регистр текущего адреса (РТА <0...6 > );

- выходной буфер микрокоманды (М£);

- блок синхронизации (БС);

- схему обмена;

- регистр управления (ГУ < 0...3 >' ).

ПДО - предназначена для хранения и считывания микрокоманд. Связи в подматрицах ПЛМ ("кодировка" подматриц и слоя инверторов) запрограммированы под систему команд УЧПУ "Электроника НЦ-31 и жестко записаны в процессе технологического изготовления БИС УП.

На регистры РК и ГС принимается и хранится поступающая извне информация (крмандные слова и признаки результатов операций). Необходимость смены информации в РК и ГС определяется состоянием триггеров "конец команды" (КК) и "ждем смену состояния" (ЖС), находящихся в регистре РУ.

- 12 -

OUIMI); У1 - матрица. 27x100 (ПЛМ2); УП -

микро ко-

манда

Парафразные выходы ГК и PC подключены ко входам подматрицы ШШ. На регистрах ГСА и РТА организована внутренняя обратная связь в УП. Записью информации в РТА из РСА управляет триггер FT "ЗВ2".

ЕС - формирует внутренние сигналы, стробирующие схему обмена, РУ, РТА, РСА, блок ПШ, начало и окончание выдачи микрокоманд в внешних сигналов, таких как "синхронизация" (42) и "конец команды" (КК). На входы ЕС УПА поступают внешние сигналы "информация выдана регистру команд" (ВИС) и 41, сигнал от устройства управляемого БИС УП (в данном случае от ААУ). Этот сигнал определяет момент приема к исполнению выданной из БИС УП микрокоманды. Кроме внешних сигналов на ЕС подаются внутренние сигналы:

ЖС - сигнал, приостанавливающий выборку микрокоманд и разрешающий ее только после приема информации на ГС БИС УП;

КК - конец команды (или конец микропрограммы); приостанавливает выборку микрокоманд до прихода ВРК. По сигналу ВПК изменяется содержимое регистра РК.

На рис.З представлено, каким образом используются выводы БИС УП в УПА. На входы РК заведены информационные разряды магистрали М < I5...0 > , прошедшие усилители командного слова. 4- разрядная магистраль состояния объединяет выходы ГС ААУ в ОАУ и вход ГС УПА. Это позволяет условно расширить вход регистра команд УПА с целью приема признаков результата выполнения операции для организации ветвлений в микропрограмме выполнения команд условных переходов. Выход РЫК УПА подключен к микрокомандной магистрали ААУ. Кодировка микропрограмм УПА в мнемокодах и двоичных кодах приведена в приложении.

5.3.2. Операционный подпроцессор (ОПП) ОСП представлен на рис.З и включет в себя:

- операционное арифметическое устройство;

- микропрограммную управляющую память опере-пн о иную;

- схемы синхронизации работы ОПП в составе СБ.

Операционный подпроцессор предназначен для хранения, обмена и обработки операндов в командах, где имеется код операции над числами.

5.3.2.1. Операционное устройство OiJi выполнено на одном БИС АУ - K588BCI. Распределение регистров ОАУ приведено в табл.6.

В однословном формате ОБ ОАУ функционирует автономно и выполняет содержательные действия, указанные в поле КОП командного слова. При об работке двухсловных операндов микрокомандной загрузкой регистра РН£, ОАУ настраивается на роким "старший". При этом регистры ОАУ используются как старшее поле для хранения и обработки <31...16> разрядов информации. (Подобной перестройкой ААУ настраивается на режим "младший" и часть его регистров используется как младшее поле для хранения и обработки <15... О > разрядов информации). Признаки результата операции при обработке двухсловных операндов формируются и выдаются в магистраль состояния из ГС ОАУ.

Как показно ка рис.З канал KI ОАУ подключен к магистрали М<15...0> . На входы И«К поступает 12- разрядная микрокоманда с выходов демультиплексора микрокоманды СИ, сопровождаемая сигналом "начать" Н ОАУ. Цепи переноса и сдвига СО, с5. CI6, сТб ОАУ соединены с соответствующими цепями ААУ, образуя в ОБ единый 32-разрядный арифметический блок.

13 -

5.3.2.2. Микропрограммная управляющая память операционная выполнена на двух БИС УП - К588ВУ1--0101 и К588БУ1-0102, имеющих различные типы кодировок. В ОШ принято следующее размещение микропрограмм выполнения действий над. операндами:

У.П01

Микропрограммы выполнения унарных, бинарных команд, команд пересылок, команд безусловных переходов

УП02

Микропрограммы выполнения рада регистровых команд ^операции с триггером "Р", инверсии регистров, сдвиги), команд передач управления, команды умножения, команды обработки двухсловных операндов.

На рве.2 представлено подключение УП01 и 1II02 в 01ш. Входы ГК УП01 и УП02 запараллелены и соединены с магистралью М < 15...О> . Выходы ШК аппаратно объединяются на демультиплексоре микрокоманд ОАУ,. Вход ГС УЕ02 используется для однонаправленного приема признаков результата выполнения операций и организации микропрограммных ветвлений в командах условных переходов. Кодировки микропрограмм УЕ01 и ’П02 даны в приложении.

5.3.2.3. Описание схем синхронизации ОТ1 дано совместно с описанием схем синхронизации АШ в составе ОБ. Схемы синхоонизагми ОПП и АШ предназначены:

- для управления параллельной оаботой под-проиессоыов при выполнении действий над двухсловными операндами и команды умножения,

- для предотвращения конфликтных ситуаций обмена подпропессоров по магистрали М.

Схемы W Ж'! и Ф1 УПА "НАЧАТЬ" ОАУ и "НАЧАТЬ” ААУ, ИИЗ ЛЬ” PC - управляются по сигналам схемы перестройки формата слова ОБ. Схема перестройки формата слова ОБ управляется сигналами микропрограммной управляющей памяти БЫ. Синхронизация параллельной работы поддроцессоров обеспечивает одновременность перехода ОАУ и ААУ к выполнению микрокоманд микропрограмм обработки слов двойной длины. Данный вид синхронизации обеспечивает достоверность информации на линиях переноса в сдвига ОАУ и ААУ при выполнении содержательных действий над 32-разрвдными операндами.

Схемы блокировки адресного подпроцессора и приостанови операционного управляют поочередным подключением информационных каналов ОаУ и ААУ к внутренней магистрали Ы ПЩ. В случае выдачи адреса операнда и АШ в магистраль М и параллельной микрокомандной настройки ОПП на прием операнда в АК ОАУ, возможна конфликтная ситуация приема кода адреса ААУ как значения операнда в ОАУ. Следующий вид конфликта обмена по магистрали ‘i-смешение кода адреса ячейки памяти УЧПУ, отведенной под запись операнда или результата операции, непосредственно со значением самого записываемого операнда. Недопустимость описанных "столкновений" в ма

гистрали М достигается поочередной блокировкой ОШ или АНЕ, производимой на основе анализа сигналов управления УПИ БЫ', состояния обслуживания запросов на информационный обмен по МНЦ, анализа фолата текущего командного слова, анализа типе следующей микрокоманды в ОШ, Блокировка АПЛ осуществляется принудительной подачей нулевого потенциала на вывод 3-2 БИС УНА. Ери этом запрещается выдача очередной микрокоманды для ААУ и происходит приостанов адресного подпроцессора. Приос-таиов ОШ выполняется прерыванием цепи прохождения сигнала И ОАУ . Отсуствие строба "Начать” приостанавливает работу операционного АУ.

5.3.3. На функциональной схеме, представленной на рис.6, приведены узлы и схемы БЫ’. БЫ является основным структурным блоком процессора, с помощью которого осуществляется начальный запуск процессора, микропрограммный переход к подпрограммам обработки прерываний и синхронное обслуживание основного процесса, выполнения команд в ОБ. Управляющие сигналы БЫ’ анализируются и используются во всех блоках ЕРД.

5.3.3.1. Микропрограммная управляющая память БНУ (рис.6)

УЕИ формирует микрокоманды управления обменом информацией по внутренней магистрали М, и межмагистральным обменом М ЫНЦ.

Входы регистра команд РК УПИ подключены к ма-магистрали М для приема командных слов. Выходное поле регистра микрокомандрШ УЛИ представляет собой совокупность отдельных управляющих сигналов (микроприказов):

- БА - признак предстоящей выдачи адресной инфор-. маиии в магистраль МШ. Используется для активизации схемы захвата ASHE (СЗМ ИБ);

- ЧТ - сигнал-идентификатор вида обмена ЧТЕНИЕ; -ЦТ?/. - сигнал-идентификатор вида обмена ЧТЕНИЕ с последующей записью результата операции по исходному адресу;

- ЗЕ - сигнал-идентификатор вида обмена ЗАПИСЬ;

- УМ - признак выполнения команды кодового умножения, используется для перестройки формата. слова ОБ;

- МК<6>- микроприказ, совместно закодированный с сигналом ЕА в комбинациях:

- Ж < 6 > & ВА - сигнал "Сброс" (нач.установка ОБ);

- МК <6>& ЕА - сигнал "Конец" (К), извещает о предстоящем завершении микропрограммы;

- МК<7>- микроприказ, совместно закодированный с сигналом БА в сочетании МК < 7>Д ВА-сигнал предварительной блокировки 01.11 (ПБ). МК < 7 > в сочетании с микропри-казом МК < 8 > управляет также схемой ЕКЬП БЕУ;

- МК<8>- микроприказ, совместно закондированный с см1налом ЧТ в комбинации МК < 8 > & ЧТ-сигнал блокировки А1Ш (Б).

- МК<9>)- группа микроприказов, управляюилх об-- МК<1О>|меиом регистров ГСЬ (РР и Р“) с магистралями М и МНЦ;

- 14 -

I - управляющие сигналы; II - сброс; IU - узел фиксированных векторов; ХУ - узел псевдокоманд; У -узел пуска ПЩ; У1 - у5ел ф! УЛИ; УП - узел оста-

нова ПРЦ, YJU - узел строба команды; IX - Узел останова СБ; X - магистраль М <15...О> ; XI - кода псевдокоманд; XII - прерыватель ТИП; Х)П - установка

- ШУ - сигнал установки регистра РР ПН1 в "I" состояние;

- МУ - сигнал установки регистра Bi ПРЦ в "I" состояние;

- МС - сигнал установки FM ПШ в ”Э" состояние.

К регистру состояния ГС УПИ подключены сигнальные линии ПЕЕР и СШ ОБМЕНА. Анализ содержимого ГС выполняется на момент приема очередной команды в УПИ, и по результату анализа может быть организован микропрограммный переход к обслуживанию внешних или внутренних прерываний.

В отличие от микропрограммной памяти ОБ (УПА; УП01.2) микрокоманда УПИ предназначена для нескольких ведомых (исполнительных) устройств. Управляющие сигналы УПИ в ведомых устройствах, таких как Г1КВП БЕУ, СК МНЦ и СК М БНУ, СЗМ ИБ и др. подключенных к магистрали М и МНЦ, предотвращают одновременную выдачу информации от нескольких активных источников в одноименные разряды магистралей М и МНЦ. Интегрированный сигнал ответа о приеме и исполнении микропрмказов текущей микрокоманды УПИ формируется схемой 41 УПИ. Входными сигналами для схемы 41 УПИ служат:

- сигнал квитирования магистрали М-ПМ, свидетельствующий о завершении информационного обмена по магистрали М текущим, активным исполнительным устройством;

- сигналы интерфейсного блока, характеризующие текущее состояние обменов по магистрали МНЦ.

5.3.3.2. Схема формирования кодов псевдокоманд и векторов прерываний.

ПКЕП выполняет функции формирования: а) кодов псевдокоманд:

- пуск начальный 1ДАЧ

- прерывание (ПРЕР или сбой питания) Г.РЕР

- код текущей команды отсутствует в

списке команд УЧПУ НКОД

- ошибка обмена по магистрали МНЦ ОШ

- обмен (ЧТЕНИЕ/ЗАПИСЬ) с регистра-

ми ГСВ ПРД FST

б) фиксированных векторов для соответствующих причин прерывания:

ail - 0C0357g

АСП - 000277g

НКОД - 000377g

Двоичные коды перечисленных псевдокоманд (см,табл.7) используются в микропрограммной уп-раьлдюоей памяти ПЩ (УПА; УП01, 2 и УПИ) для формирования микропрограммных частей выполнения процедур внешних и внутренних прерываний.

Коды фиксированных векторов в дальнейшем принимаются в ААУ ОБ и соответствуют адресам памяти УЧПУ, с которых начинается программная обработка тех же видов прерываний.

Входными сигналами для схемы ПКЕП являются сигналы общей установки ПЩ, сигналы, характеризующие активизацию БНУ, сигналы прерывания процессора и микроприказы УПИ. Выходные сигналы ПКВП подключены к разрядным линиям магистрали М.

5.3.3.3. Схема управления СУ2 приведена на рис.6 и содержит:

- схему запуска процессора;

- схему останова процессора;

- 15 -

Ряс. 7. Функциональная схема. ЕНУ:

I - магистраль АД МНЦ; П - усилители адреса; Ш -узел СК МЖ1; ХУ - поправленье т-.>*<му гадим; У - да адреса (ССА); У1 - узел управления ЕНУ; УП • анализ номера регистра, УШ - буферный регистр номера КБ; IX - узел обращения к РСН; X - узел обра-

- схему приостанова ОБ;

- схему синхронизации приема командных слов и кодов псевдокоманд на РК 5П ПН).

Комплексное взаимодействие перечисленных fкем обеспечивает выполнение режимов работы про-tчссора - ПУСК, ОсТАЕОЕ, ПУСК Ш (отладка программ в диагностическом режиме).

Схема запуска процессора по входным сигналам ПУСК БНУ и СБРОС БЕУ формирует обобщенный сигнал пуск процессора $ По сигналу 3* В Микропрограммной управляющей памяти ПН) прекращается выборка любых последовательностей микрокоманд и формируется признак готовности БИС УП (КК) к приему новой команды. По данному признаку в схеме синхронизации приема команд на входы всех регистров команд БИС УП вырабатывается сигнал ВИС Сигнал ВЕК обеспечивает одновременность приема командного слова в УПА, 11101,2 и УЛИ.

Схемы останова процессора и останова ОБ управляют пошаговые исполнением команд в процессоре, приостановок ОБ при ветвлении ситуации НКОД и динамическим остановом ПН). Схема останова СБ используется также для управления очередностью информационных обменов АШ и ЯШ по магистрали Ы. Схема останова ОБ после выполнения текущей команды блокирует работу АПЛ и ОШ. При приеме новой

Щвния к КВ; XI - учел начальной установки ПИ1; XI - .узел прерывания, Ж - увел РСН; ПУ - узел СК М; ХУ - магистральные вентили; ХУ1 - установка; ХУЛ - пуск, ХУШ. - прерывание

команды и истечении времени выборки первой микрокоманды УЛИ по управляющим микроприказам последней, при необходимости, производится блокировка работы СПИ и А1Ш. После этого по сигналам схемы останова ОБ разрешается выполнение микропрограмм новой команды в ОБ. Так происходит управление вычислительным процессом в ОБ по микропрз-казам УЛИ БВУ.

5.3.4. На рис.7 приведена функциональная схема блока наружного управления. БНУ обслуживает обращения к ПН) по системным адресам его регистров (группы РСН и FCB), обеспечивает построение многопроцессорных (до четырех 1ВД) конфигураций УЧПУ , используется в диагностических программах тестирования процессора. Активизация БНУ пооисходит при приеме из магистрали МНЦ кода адреса, совладеющего с системным адресом одного из программно-доступных регистров ПРЦ.

5.3.4.1. Схема опознания адреса

По интерфейсному сигналу МНЦ - ОБМЕН (ОБМ) в ССА выполняется сравнение кода собственного адреса процессора с кодом адреса, выданным в МНЦ активным устройством. Адресное поле регистров процессора (собственный адрес) принято равным:

- 16

Разряды АД магистрали МВД

Код адреса

15 14 13 12 II 10 9 8 7 6 5 4 3 2 1 0

I I I 10 О ООХХХХХХХ

ВУ-признак Класс обращений устрой-к регист- ства рам ПН! и НГЦ периферийных устройств

й # регистра

ИЦ процессора

При равенстве старших разрядов указанных адресов (разряды <15...6> ) происходит дальнейшая дешифрация адресного поля с целью доопределения группы регистров ПИ1, которой предназначено обращение по МНЦ.

5.3.4.2. Схема обращения к регистрам РР и РЫ (СЧЗ РСН) приведена рис.7.

В случае обращения к регистрам системным наружным (РР и ГМ) ССА совместно со схемой управ

ления БНУ запускает схему СЧЗ РСН. В состав схемы СЧЗ FCH входят:

- схема обращения к РСН, фиксирует факт обращения го МВД к регистрам РР и ГМ;

- схема РСН,содержит одноразрядные регистры РР и ГМ с логикой чтения/записи информации;

- схемы формирования сигналов-идентификаторов (квитирования обмена по магистралям МВД (СК МВД и М (СК М).

Информационный обмен с регистрами РР и HJ по магистрали МВД выполняется без прерывания исполнения программы в ПН1. Регистр режима текущей работы процессора - РР, используется для управления пошаговым (покомаядным) выполнением программа и для исполнения процедуры ОСТАНОВ. Регистр маскирования процессора ~ ГМ блокирует либо разрешает прерывание ПЩ по магистрали МНЦ. Текущее состояние ГМ учитывается, в частности, при анализе приоритетности (очередности поступления) запросов ка обработку внешних и внутренних причин прерывания процессора.

Коды псевдокоманд процессора

Таблица 7

Наименование процедуры Мнемокод Двоичный код Смгнал-инипиатор процедуры Примечание

ПУСК НАЧАЛЬНЫЙ СШИБКА ВЕДОМОГО ВНЕШНЕЕ ПРЕРЫВАНИЕ АВАГИЯ В СЕТИ "НЕСУШЕСТВУЮЕАЯ*' команда ОБРАЩЕНИЕ К РСВ ПНАЧ ОШВ ПРЕР АСП ' У НКОД РЕГ 0 I0X ОХХ ХИН НХХ XXX 0 00Х IXX XXX XXX XXX 0 OIX IXX XXX XXX XXX 0 0IX ОХХ XXX XXX XXX I ООХ ОХХ XXX У5У JjJ уп (Пуск) ТОЙ зпр". АИЛ ПГТ Н-номер ПН! ГСупи = XI ГСупи = 10 ГСупи = 00 р* < ч s — > О-ЗП к<з> = |1_чт у - номер ГСВ

СК МВД вырабатывает интерфейсный сигнал ОТВЕТ (ОТВ) при обращении к регистрам РСН по чтению/записи по магистралям МВД. СК М формирует сигнал ВМ в случае чтения содержимого РР и Hi по магистрали М или ПМ - при выполнении записи информации из разрядов М <4,0> соответственно в ГМ и РР. Указанные сигналы сопровождают информационный обмен в командах вида ГО ГОН.

5.3.4.3. Схема обращения к регистрам РОВД , РВД1 , РУС, РСЧК, HIP (СЧЗ РСВ) приведена на рис.7. В состав СЧЗ РСН входят:

- схема обращения к РСВ, запоминает наличие обращения по МВД к регистрам группы РСВ;

- буфер номера регистра процессора, хранит номер регистра, с которым производится информационный обмен;

- схема анализа некорректного адресного обращения;

- схемы квитирования обмена СК МНЦ и СКМ.

Обмен по чтению/записи с регистрами ОБ (группа РСВ) выполняется только в режиме ОСТАНОВ ПЩ

При адресном обращении к процессору параллельно с дешифрацией адресного поля МВД в ССА осуществляется прием младших разрядов АД < 5...0 > &2ВД в буферный регистр. Наличие обращения к РСВ запоминается схемой "Обращение к РСВ". Далее происходит’ - анализ текущего состояния функционирования ПЩ;

- анализ обращения к разрешенным номерам регистров ОБ;

- формирование сигнала прерывания процессора ПГТ.

Разрешенными номерами регистров ПЩ являются системные номера регистров РОН 0...I7; ГОД 0,1, РУС, РСЧК, RIP операционного блока (см.табл.3). Пси обнаружении "чужого" номера регистра сигнал ПГТ не вырабатывается и по "умолчанию" ВДУ и РД в УЧПУ срабатывает таймер "зависания”, расположенный в модуле АМТ. Таймер "зависание МВД" фиксирует отсутствие абонента с заданным адресом (ведомого устройства) на МВД и по истечении фиксированного интервала времени (~ 50 мкс) после

17 -

начала обмена форлирует сигнал ОШ. Таймерный сигнал ОШ относительно I1HJ, может означать:

- адресное обращение к процессору без предварительного указания процедуры ОСТАНОВ последнему;

- адресное обращение по "несуществующему" номеру регистра процессора.

При соблюдении правил обращения к регистрам РОВ по сигналу ПИ1 происходят запуск блоков БВУ, ОБ и ИБ ПИ! на однократное выполнение процедуры ОБМЕН С РЕГИСТРАМИ РОВ. По сигналам схемы управления ШУ и схем СК МНЦ, СК Ы обеспечивается информационный доступ в/из магистраль М и сопровождения обмена сигналами квитирования - НИ, ПМ для магистрали М или ОТВ для магистрали МНЦ.

5.3.4.4. Схема формирования признаков внешних и внутренних прерываний процессора (рис.7)

СПИ состоит яз схем формирования сигналов прерывания и пуска процессора. Обслуживание прерываний в ПН! подразделяется на три фазы:

I - аппаратная реализация обслуживания, выполняется в СНЕ;

11 - микропрограммный уровень, выполняется блокам» ОБ ИБ, БВУ;

N - программный уровень, выполняется программами обслуживания прерываний.

Входные сигналы ОШИБКА БКЦОМСГО (ОШВ), ЗАПРОС НА ПРЕБЫВАНИЕ (3IP), АВАРИЯ СЕТЕВОГО ПИТАНИЯ (АСП) преобразуются в СПП, с учетом очередности их поступления и приоритетности обработки, во внутренние сигналы для блоков процессора - ПРЕР и ОШ. Анализ наличия этих сигналов выполняется в PC УЛИ БВУ во время приема очередной команды рабочей программы.

Далее по ммкроприказам УЛИ схема пуска ПН! организует "очистку" ОБ и запускает схему ПКВП БВУ. По коду псевдокоманд ПРЕР или ОШ, принятому в микропрограммную память процессора (УПА, УП01.2 УЛИ; формируются микропрограммные части дальнейшей обработки прерываний (11 фаза).

5.3.5. Интерфейсный блок (ИБ)

Функциональная схема интерфейсного блока приведена на рис.8. ИБ обеспечивает информационный обмен процессора с другими модулями УГЛУ, согласовывает интерфейсные сигналы магистралей М ШЦ и МНЦ УЧПУ, применяется для умощнения сигналов информационно-упралляющих линий процессора. В состав ИБ входят:

- схема информационного коммутатора (ИК);

- схема захвата магистрали МНЦ (СЗМ);

- схема формирования сигналов сопровождения обмена по магистралям М и МНЦ (СК ИБ);

- схема арбитра магистрали МНЦ (AM).

АД MHU РЗП П ЗЛР РЛР ПТЗ ОБИ ОТВ

Рис. 8. Функциональная схема ИБ:

I - магистраль МНЦ; U - направление коммутации М - МНЦ; IU - узел управления ИК и квитирования магистралей М, МНЦ; 1У - узел запроса ЛБЦ; J -

узел арбитра МНЦ, il - узел анализа линейного разрешения и разрешения прерывания; УП - узел подтвержденья запроса и фиксации периода обмена

5.3.6.1. Информационный коммутатор выполняет функции:

- трансляции адресной инфюрмации из магистрали М В МНЦ;

- коммутатора магистралей Млр^МНЦ для обмена one г-жами между СБ ПН! и модулями УЧПУ.

В состав 16- разрядного ИК входят непосредственно элементы коммутации, реализуемые на двунаправленных шинных усилителях типа К589АП26, ж схема управления ИК. Схема управления по микроприказам УЛИ БВУ, ГСВ БНУ и сигналам сопровожде

- 18 -

ния обменов определяет -направление передачи информации -- М МВД или МНЦ М.

ИК инвертирует информационно-упраьляиюхие сигналы и выполняет электрическое сопряжение магистралей М и МНЦ по уровням ТТЛ ИС. Выходные передатчики ИК построены по схеме с открытым коллектором и обеспечивают работу с согласованными линиями. В отключенном состоянии двунаправленные шинные усилители ИК позволяют выполнять в процессе вычисления независимо от текущего состояния обменов по магистрали МНЦ. Этим достигается возможность построения многопроцессорных конфигураций УЧПУ.

5.3.5.2. Схема захвата МНЦ (рис.8)

выполняет стандартную процедуру подключения процессора к МНЦ при его обращениях к устройствам УЧЕТУ.

СЗМ включает в себя:

- узел собственного запроса ПЩ;

- узел анализа линейного разрешения (А1Р);

- узел подтверждения запроса и фиксации периода обмена;

- узел арбитра магистрали МНЦ (AM).

В состав каждого из перечисленных узлов входят элементы памяти и комбинационные логические схемы, обеспечивающие хранение и обмен интерфейсными сигналами СЗй ИБ с другими модулями УЧПУ.

Сигнал запроса процессора на занятие магистрали МНЦ для проведения очередного обмена формируется узлом собственного запроса ЕНх по микроприказу УЕИ ББУ - ВА и при наличии адресной информации в магистрали М. Затем сигнал запроса выдается в линию ЗМ группы шин обмена "модуль-арбитр" МВД. Наличие сигнала ЗМ проверяется в узле арбитра магистрали при проведении очередного цикла назначения нового БВДЛЦЕГО УСТРОЙСТВА. Узел AM по сигналу ЗМ при отсутствии магистрального сигнала ПТЗ формирует сигнал РАЗРЕШЕНИЕ НА ЗАНЯТИЕ МАГИСТРАЛИ (РЗМ). Сигнал РЗМ последовательно опрашивает устройства УЧПУ данного приоритетного уровня. Старшее (левое) из устройств, которое выдало запрос на обмен МНЦ, блокирует дальнейшее распространение сигнала РЕМ и устанавливает сигнал РАЗРЕШЕНИЕ СОБСТВЕННОЕ (РЗМс). Данную функцию в процессоре выполняет узел АДР СЗМ.

В случае незанятости магистрали либо после завершения обмена предыдущего активного устройства, схема подтверждения запроса по логическим значениям сигналов РЗМ = I, ОБМ = ОТВ = 0 - устанавливает сигнал ЗАПРОС ПОДТВЕРЖДАЮ (ПТЗ). Сигнал ПТЗ запоминается на триггерном элементе ТгПТЗс и:

- оповещает другие модули УЧПУ о готовности данного процессора к обмену;

- обнуляет сигнал ЗМ данного процессора;

- "гасит" выходной сигнал РЗМ AM;

- блокирует выполнение нового цикла AM для

определения следующего ведущего, до начала текущего обмена.

По окончании переходных процессов в магистрали МВД и при наличии сигнала ПТЗ, СЕМ ИБ устанавливает сигнал МАГИСТРАЛЬ ЗАНЯТА УСТРОЙСТВОМ (OEM). Сигнал ОБМ:

- блокирует выход любого другого устройства на МНЦ до завершения обмена инициированного данным процессором;

- выполняет сброс Тг ПТЗс;

- разрешает проведение информационной части обмена;

- резблокирует схему AM ИБ.

После завершения обмена процессе» а СЗМ переходит в пассивное состояние. Выходы информационных и управляющих передатчиков сигналов магистрали МНЦ сбрасывает сигнал ОБМ, освобождая тем самым общую магистраль УЧПУ-МНЦ.

5.3.5.3. Схема формирования сигналов сопровождения обмена по магистрали М и Ь'ЛЦ

СК ИБ

- участвует в процессах адресного (или безадресного) назначения ведомого устройства;

- формирует сигналы управления обменом данными;

- анализирует ответные сигналы, поступающие из устройств-абонентов;

- формирует сигналы сопровождения информации для магистралей М и МНЦ.

Обмен данными осуществляется м*.вду ВЕДШЗЕМ и назначенным ЬНДОМЫМ устройствами, подключенными к МНЦ, и включает в себя три типа обмена:

- ЧТЕНИЕ;

- ЧТЕНИЕ С МОДИФИКАЦИЕЙ;

- ЗАПИСЬ.

Последовательность выдачи внешних интерфейсных сигналов ПН1 при обмене по МНЦ - ОБМ, ОТВ, ДЧТ, ДЗП и т.п. выполняется в соответствии с временными диаграммами обменов, приведенными в техническом описании УЧПУ, раздел "Временные диаграммы операций интерфейса МНЦ".’В сост.хв интерфейсного блока входит одновибратор (Д15), задающий длительность задержек сигналов интерфейсного обмена для формирования временных диагрг»мм.

СК ИБ выполняет также преобразование внешних интерфейсных сигналов МНЦ в сигналы-идентификаторы сопровождения информации по внутрипроиессорно/. магистрали М (интерфейс БИС):

ЕЛ - сигнал асинхронного обмене ИНФОРМАЦИЯ В МАГИСТРАЛЬ М ВЦПАНА (признак достоверной информации в магистрали М);

ГМ - сигнал асинхронного обмена ИН5ОВ*АЦИЯ ПО МАГИСТРАЛИ М ПРИНЯТА (признак окончания записи в текущее ВВДЖОЕ устройство магистрали М).

5.3.5.4. Схема арбитра магистрали МВД

ДМ предназначен для упорядочивания обменов по магистрали М, инициируемых по запросам актив

<9 -

ных модулей УЧВД. Проведение информационных обменов по разрядным линиям АД < 15...О > МВД, а также необходимость посылки переменных векторов, характеризующих причины внешних прерываний ПИ1, требуют введения строгой синхронизации очередности обменов по МВД. В УЧПУ "Электроника ВД-31? принят алгоритм арбитража магистрали, при котором сигналы запросов не прерывание процессора (ЗПР) в процедуре безадресного назначения ВЕДОМОГО микропрограммно преобразуются в сигналы запросов на обычный информационный обмен (ЗМ). Построение единой радиальной приоритетной линии для сигналов SM и ВДР исключает эффект "гонок" и обеспечивает использование магистрали МВД с разделением времени между активными устройствами УЧПУ.

5.3.6. Устройство ПЗУ

На рис.9 приведена функциональная схема ПЗУ. ПЗУ включает в себя:

- накопитель;

- схему опознания адреса;

- регистр адреса;

- схему связи с внутренней магистралью процессора по управляющим сигналам.

5.3.6.1. Работа устройства ПЗУ

Работа устройства ПЗУ происходят в соответствии с интерфейсом внутренней магистрали процессора. Диаграмма сигналов интерфейса представлена на рис. 10. Сигнал ЧТ ПЗУ открывает РгА я триггер опознания на запись» Сигналы ТВА, ЪМ, ЧТ ПЗУ собираются по "И", и формируется строб на схему опознания. При совпадении кода заливки адреса ПЗУ с установленным на магистрали ходом адреса, поступающим из ПН1 (для ПЗУ-А < 0 > , А < I > , А < 2 > , А < 3 > = 0)с выхода схемы опознания.выраоатывается строб записи логической ' 1" в триггер опознания, а также подается для выработки признака обращения к ПЗУ сигнала АПК (АПК). Сигнал АПК подтверждается признаком опознания, поступающим с триггера опознания и держится в течение всего цикла обмена. При окончании процесса опознания ПЗУ вырабатывается признак окончания приема адреса устройством ПЗУ - сигнал КП, после чего процессор сбрасывает сигнал ТВА, Ш и адрес. По сбросу сигнала ЕМ формируется сигнал блокировки приема ЭД I и формируется сигнал ЬК на микросхемы накопителя П<ЗУ, при этом выходы микросхем накопиталя ПЗУ переходят в активное состояние из состояния высокого выходного имгедаяса. Через время, определяемое временем выборки микросхем накопителя ПЗУ, на магистрали появляется истинная информация и при достижении фронтов считанных информационных сигналов 0,9 своего значения вырабатывается сигнал КВ (код выдан). Задержка выдачи сигнала КВ на время выборки информации из ПЗУ обеспечивается линией задержки. Процессор сбрасывает сигнал ЧТ ПЗУ в устройство ПЗУ переходит в исходное состояние, при этом сбрасываются сигналы КВ, АПК, КП, ВК и микросхемы накопиталя ПЗУ переходят в состояние высокого выходного импеданса. На этом цикл считывания заканчивается.

Рис. 9. Функциональная схема ПЗУ:

I - триггер опознания адреса ПЗУ-; U - перемычки А ПЗУ; Ш - схема опознания адреса; 1У - регистр адреса; У - адрес; У1 - накопитель Ь Кх16 Сит; УП - дачные

zze

м

<15.О>

КП

ЧТ

ТВА

АПК

строб РГА вкпзч

Рис. 10. Временная диаграмма работы устройства;

I - адрес; U - информация не определена; К - данные

5.4. Подключение ячейки ПН1 к магистрали МНЦ и управление процессором

В УЧПУ "Электроника НЦ-31" предусмотрено подключение четырех процессоров к магистрали МНЦ - процессоры П1, П2, ПЗ, П4. Практически спроектирована однотипная принципиальная электрическая схема модуля ЦЩ с возможностью пере-компановки монтажных перемычек:

- I...12, определяют собственный адрес процессора (П1 - 00, П2 - 01, ПЗ - 10, П4 -П4 - II);

- 13, 15, обеспе- прохождение сигнала

РЗМ, т.е. задают "геометрический" приоритет процессору при обменах по магистрали МНЦ;

- 14, 15, задействуют работу схемы AM ИБ в центральном процессоре системы;

- 16...18, коммутация линии 3I1P к процессору, обслуживающему данный вид прерываний;

- 19, 20, разрешение формирования сигнала начальной установки УСТ по сигналу ЛИП БП только в центральном процессоре системы.

В УЧПУ "Электроника НЦ-зГ’ использована однопроцессорная конфигурация с распайкой монтажных перемычек в соответствии с указаниями на принципиальной электрической схеме ПН1 3.050.005 ЭЗ.

Возможность межпроцессорного взаимодействия модулей ПН1, подключенных к магистрали МНЦ, обеспечена организацией адресных обращений МНЦ к регистрам процессоров по их системным номерам. Такое взаимодействие включает чтение/запись всех программно-доступных регистров ПШ. Процессор может управлять своим собственным состоянием по магистрали М при выполнении команд системных пересылок вида РО ШН и команд ЕДАТЬ, СТОП.

Рис.II иллюстрирует переходы состояний процессора между рабочим режимом и режимом приостановки (ожидания внешнего воздействия).

Рис. II. Диаграмма состояний ПЕЦ НЦ-31-

I - ПНАЧ (включение питания или АСП); II - ждать (команда ПИ1); 111 - стоп (команда ПШ); 1У - запись О вВ1 по МНЦ, запись I в РР по МНЦ; У -запись I в FM по МНЦ, запись I в РР по МНЦ; У1 -рабочий режим; УП - режим ВДАТЬ; УШ - режим СТСП; IX - выполнение команд в ПЩ; X - чтение/запись регистра РСВ ПЩ по МНЦ; XI - чтение/запись регистров РСН по МНЦ; XII - внешние прерывания ПЩ по МНЦ (при РМ=О)

Прерывание выполнения текущей прогршлмы процессора может быть вызвано внешними (внешнее прерывание) или внутренними командами (внутреннее-прерывание) по отношению к процессору причинами.

Причиной внутреннего прерывания может быть несуществующий код команды НКОД. Причинами внешних прерываний могут быть:

З ПР - запрос на безадресное обслуживание;

ЕЕГ - обмен по чтению/записи с регистрами

РСВ;

О Ш - ошибка при приеме/выдаче информации абонентом МНЦ или отсутствие абонента с заданным адресом на МНЦ;

АСП - авария сетевого питания.

Ошибка Прерываний в ПЩ заключается в выполнении микропрограммной части в последующем переходе к подпрограмме обработки по конкретной причине прерывания. Микропрограммная часть выполнения процедур ПРЕР, ОШ, НКОД, АСП состоит из:

- записи текущего значения РСЧК в стек;

- формирования адреса вызова соответствующей подпрограммы обработки по вектору прерывания. -

При выполнении процедуры АВАР/Я СЕТЕВОГО ПИТАНИЯ обязательный условием является выполнение команды СТОП в конце подпрограммы обработки сбоя питания. После восстановления питания (или при начальном включении питания) процессор автоматически выполняет процедуру НАЧАЛЬНЫЙ ПУСК.

5.5. Система команд процессора "НЦ-31”

В данном разделе приводятся освоенье сведения по системе команд процессора, необходимые для понимания последующего алгоритмического описания выполнения микропрограмм отдельных команд. Подробное изложение системы команд дано в техническом описании УЧПУ "Электроника НЦ-31*'

5.5.1. Виды и форматы данных

Команды ПЩ "НЦ-31” рассчитаны на непосредственную обработку:

16- разрядных кодов (слов);

8-разрядных кодов (байтов);

- чисел с фиксированной запятой, представленных одним или двумя словами.

5.5.2. Типы адресаций

Программа процессора выполняется в следующих областях памяти и УЧПУ:

- адресуемых регистрах непосредственно ПШ;

- двух сегментных данных;

- сегменте команд (программы);

- стеке;

- адресуемых регистрах внешних устройств (БУ’).

Типы адресации г виды операций в адресных командах едины как для ячеек оперативной памяти, так и для регистров ЬУ. Адресация данных в командах процессора - математическая (относительная). Для этого в составе ПЕЦ имеются две базы данных -два регистра (РБДО и БЕЛ), задающие начадьпые (базовые) физические адреса двух сегментов даннчх, Заданный в команде математический адрес является

21

адраоом относительно той или иной базы. При выполнении каждой команда физический адрес формируется из указанного математического адреса и физического адреса базы. Адресация команд - как относительная, так и физическая (абсолютная).

Адресация данных и команд процессора "Щ-31и разделяет сегменту программ от сегментов данных, повышая эффективность программирования в улучшая работу упр шлющих (операционных) программ. Перечень типов адресации данных и команд приведен в табл.8. Разбиение адресаций по группам - приведено в табл.9.

5.5.3. Форматы команд

Форматы команд ПЩ ”1111-31“ приведены в табл.II.Олерации команд форматов даны с помощью сообщенных операторов. Состав конкретных операций приведен в табл.10. Основной размер команд -однословный. При двухсловном размере во втором командном слове находится дополнительная информация кадрес А, константа С и т.п.). Вся система команд разбита на семь групп форматов. Каждая группа подразделяется на форматы, имеющие свои номере в группе. Группы, как правило, различаются между собой типами адресаций, форматы - группами операций. В пределах одного формата команды имеют единое строение командного слова, состоящего из нескольких поименованных полей.

Форматы Д

Сюда входят команда с короткой прямой адресацией операнда в сегменте данных [Дд] . Разряд П в командном слове указывает номер сегмента данных, признак X определяет направление засылки результата операции: на РСН (при 3£= 0) или в память (Э?= 1). Формат Д1 составляют операции иересылки. Один из операндов - на РОК, номер которого указан в поле I, второй операнд - в ячейке памяти, адрес которой указан полем Д и разрядом ц. В формате Д2 определены алгебраические операции. Код операции задан в поле АЛ, адрес пер-jz'i-o операнда указан в п и Д, второй операнд -на регистре РО.

Форматы ЕУ

Код операции команд передачи управления указывается в поле ПУ. Формат ПУ1 составляют команда

передач управления с относительной короткой адресацией и команда ПОС с абсолютной короткой адресацией J {д] . Короткий адрес указан в поле {/Д} . В формате ПУ2 определены команда передач управления с адресациями, составляющими группу М3: ( {Pj} / {а} />->/{$])- Тип адресации кодируется в поле М3, поле 3 указывает

номер РОН, содержащий адрес перехода при адресация /РiI , либо находятся нули при /а] и

ного умножения. Формат РР4 составлен из команд регистровых пересылок.

Форматы ПМ

Сюда входят команда работы с памятью и адре-сгпиямв группы MI: ( fPi 1 / [+Pi] / [А] / [Pi+ А]/ [Pj -]/ u_. /uu/u-u).

Тип адресации кодируется в поле MI. В формате EJH определены команда взаимных пересылок Р(Ж - память В поле 3 указан номер РСН, участвующего в адресации, или находятся нули при адресации [а] . Признак ЗС задает направление пересылки: при 2£ = 0 - память —РЖ, номер которого в поле I, при Z - I - РЖ — память. В формате ПМ2 определены алгебраические и байтовые операции, разделяемые признаком р. При 26 = 0 результат операции заносится в РЖ, при I - в память. Кроме того, для некоторых операций с.общим кодом БА признак JE их разделяет. Первый операнд берется из памяти. Для всех адресаций MI, кроме [А] , в полгЗ указан номер РЖ, участвующего в операции, второй операнд берется из РО. Для адресаций [а] второй операнд берется из любого РОН (его номер -3). В формате ПМЗ определены унарные операции над памятью. В поле 3 - нули, при адресации [а], или номер РЖ, участвующего в других адресациях MI.

Форматы ПР

Объединяют команда работы с константами из программного сегмента с адресациями группы М2: (С/ {РЯ t+pz] "} Тип адресащ,и кодируется в поле М2. В формате ПР1 задаются пересылка констант на РЖ, номер которого указан в поле 1. Если константа следует за первым командным ’словом (адресация С), то в поле J - нули, при остальных адресациях М2 - номер РОН, участвующего в адресации. В формате ЕР2 определены алгебраические (^ = I) и байтовые (= О) операции. При адресации С операции могут идти с любым РЖ (его номер в 3 ). при остальных адресациях - только о РО (при этом поле 3 указывает номер адресующего РЖ).

Форматы Р

Данные форматы объединяют разнообразные команда с указанием одного РЖ, номер которого указан в поле 3 . Формат PI определяет унарные операции на любом РЖ. В формате Р2 заданы операции сдвига РЖ на I разряд. В формате РЗ определены арифметические операции над двумя двухсловными операндами, размещенными над РО, PI и на двух других РЖ, номера которых заданы в полеЗ . При О результат операции заносится на РО, FI, а при X. = I - на другою пару РСН. В формате Р9 задана одна команда ЕМЗ - "размножение знака" содержимого РЖ (его номер в 3 ).

Форматы РР

В этой группе объединены команда бинарных операций с оперсидами на РОН, номера которых указаны в полях 1,3 .В формате РР2 определены алгебраические, (J* = I) и байтовые ( = 0) опе-

рации. В формате РРЗ определена команда специаль-

Форматы ОС

Объединяют так называемые команды операционной системы. В формате 0CI определены команда пересылок системных регистров между РО и стеком (вид пересылки определяет разряд X. : при <£ = О - пересылка CPj- - РО, при еС= I - пересылка

22 -

CPi - S ) • Направление пересылки определяется разрядом 9С : при 3?'= О - СР» РО или5-*-СР^, приз? = I - Ро -* СР^ ; CPj-^S). В формате 0С4 определены команды управления режимом работы

процессора.

5.5.4. Группы команд

Команды одной группы имеют, как правило, один набор операций и различаются типом адресации. По каждой группе даян форматы и операторы групп, табхяды операций и адресаций с указанием мнемокодов операций, совпадающих с мнемокодом языка ассемолера.

Типы адресации данных я команд

Таблица 8

Адресуемая область Название адресации Тип переменной Имя переменной (тип адресации) Исполнительный адрес переменной Примечание

Регистры общею назначения (РОНы) Регистровая Данные pj Номер РОЕ Адрес РСН задается четмрех-разрядныи номером или определяется кодом операции

Регистры"-процессора (системные) Регистровая Данные CPJ Састемиый номер регистра Адрес регистра задается его полным (шестираэрадным) номером или определяется кодом операции

Сегменты данных Прямая по короткому адресу Данные [Дп] РЫп+Д’. где Д' <15 > =Л Д' <8 ♦ 14> = 0, Д' <0 ♦ 7> » = К < 0 ♦ 7> Значение/п (0 или I) соответствует нулевому или первому сегменту данных в задается в коде команды

Сегменты данных Прямая по полному адресу Данные [А] РБДп + А , где п = А < 15 > Адрес А находится во втором командном слове

Сегменты данных Косвенная через регистр Данные IV РБДп + • гдеп= Pj <15> 0 Адрес находится на регистре Pj (РФ)

Сегменты данных Косвоиная через регистр с инкрементом Данные [’V РБ.О (Pj + I), гда п -4Pj +1)<15> Соде гатимое Pj сначала увеличивается на I, т.е. PJ : - Pj + 1 , а. затем используется для получения исполнительного адреса