РадиоКот >Обучалка >Микроконтроллеры и ПЛИС >Программируемая логика Altera — первые шаги >

Графический редактор MAX+Plus. Рисуем схему счетчика. Часть 1.

Ну все, надеюсь, что трафика хватило, свет не вырубился, злобный вирус не пожрал все содержимое винчестера

и у вас хорошее настроение.

Значит — продолжим.

Открываем MAX+PLUS II — для этого надо запустить файлик max2win.exe в папке с программой.

Сегодня мы начнем рисовать очень простую схему — схему 4-разрядного двоичного счетчика.

Мы нарисуем один элемент счетчика — счетный триггер, и проверим его работу на симуляторе.

Делаем так:

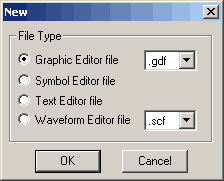

File>New

вываливается окошко

Соответственно, нам предлагают на выбор создать графический,

символьный, текстовый или диаграммный файл.

Выбираем первое — графический (Graphic Editor file).

Вываливается белоснежное оконце графического редактора. Вот именно в нем мы и будем рисовать.

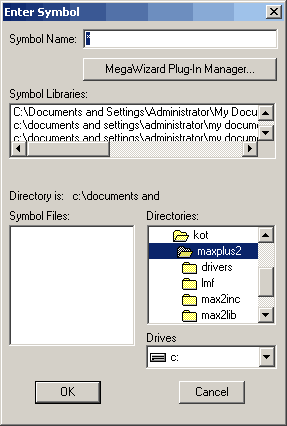

Два раза кликаем внутри этого окна. Появляется окошко «Enter Symbol».

В верхней строчке пишем «dff». Жмем OK.

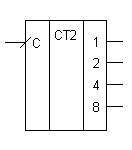

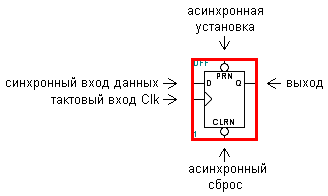

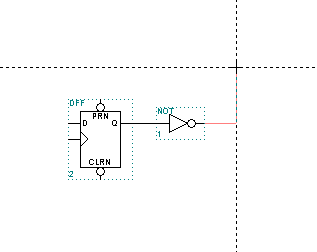

Теперь окно перестало быть белоснежно-чистым. На нем появился элемент DFF.

DFF — это синхронный D-триггер (D-FlipFlop).Он выглядит примерно так:

Что такое триггер — надо объяснять?

Совершенно верно:

Триггер — это элемент, который может сохранять поданный на него логический уровень после снятия входного сигнала.

D-триггер имеет следующие выводы:

D — синхронный вход данных, состояние на котором «захлапывается» по фронту тактового сигнала,

Clk (обозначен треугольником) — вход тактового сигнала,

PRN — асинхронная установка триггера (в лог. 1),

CLRN — асинхронный сброс (в лог. 0),

Q — выход.

PRN и CLRN — инвертированные, то есть активное состояние на них — лог.0

По умолчанию они неактивны (на них поданы единицы).

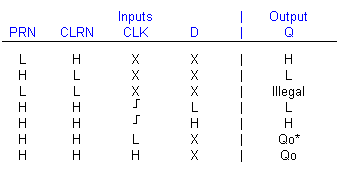

Вот таблица истинности триггера DFF, выдранная из хелпа по Макс Плюсу:

H — это «1»

L — это «0»

X — это «пофиг что»

Q0 — состояние не изменяется

Illegal — неразрешенное состояние входов

Переходим к счетчикам.

Что такое счетчик? Это такой хитрый элемент, у которого один тактовый вход и несколько выходов.

На выходах присутствует некая комбинация единиц и нулей — то есть, двоичное число.

Это число равно количеству импульсов, поступивших на тактовый вход счетчика C.

Счетчик состоит из пачки счетных триггеров.

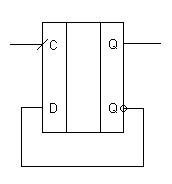

Счетный триггер — это синхронный D-триггер, инверсный выход которого замкнут на вход данных.

Таким образом, по каждому тактовому импульсу, состояние счетного триггера изменяется на противоположное.

Почему? Ну смотрим.

Допустим, сначала состояние триггера = 0.

То есть, на прямом выходе — 0, на инверсном — 1.

Значит, на вход данных D поступает 1.

При следующем импульсе на тактовом входе, состояние D захлопнется в триггер.

На прямом выходе появится 1, на инверсном — 0, и этот ноль поступит на вход D.

При следующем такте ноль на D захлопнется в триггер и так далее…

Если составить их последовательно, то можно получить счетчик. Чем сейчас и займемся…

Итак, щелкнем еще раз по пустому месту и наберем «not».

Вывалится треугольник с кружочком на носу — элемент NOT, или, по-русски — инвертор.

Зачем он нам нужен?

А затем, чтоб создать инверсный выход триггера. Как видите, у DFF только один выход — прямой.

Нас это не совсем устраивает.

Так что, собираем все мужество в кулак, расставляем элементы как нам удобно — и рисуем схему.

Для рисования схемы, на панели инструментов (слева) надо нажать на кнопочку

Рисуем…

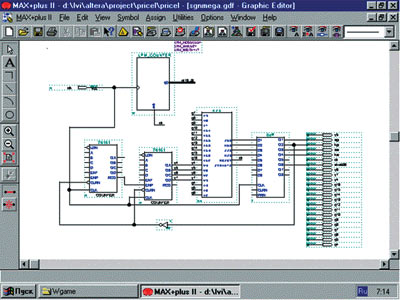

Нарисовали:

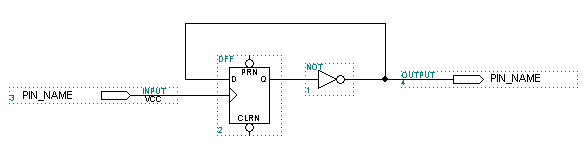

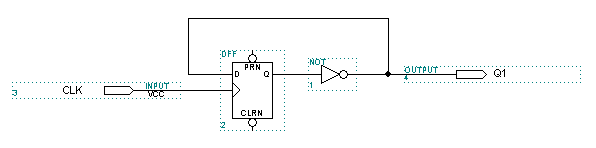

Ну, теперь вводим еще два новых элемента: input и output.

Ввели? Здорово! Дорисовываем схему:

Дважды тыкнувшись мышой в слова PIN_NAME,

вводим осмысленные названия для входа и выхода.

Названия не могут начинаться с цифры и могут содержать только буквы латиницы и некоторые

«разрешенные» символы. Мы обзовем вход CLK, а выход — Q1.

Итак, у нас образовалась схема счетного триггера со входом и выходом.

Ее уже можно компилировать и прошивать в чип.

Однако даже если вы уже спаяли макет и полны решимости

испытать все в действии — не стоит спешить:

чип недешевый, а гарантированных циклов перезаписи у него — всего ничего — 100.

Так что, давайте ка лучше, сначала проверим это дело на симуляторе.

Но для начала неплохо сохранить файл.

File>Save, вводим имя — counter.

Файл будет называться: counter.gdf.

Теперь делаем так:

File>Project>Set Project to Current File — сделаем этот файл основным файлом проекта.

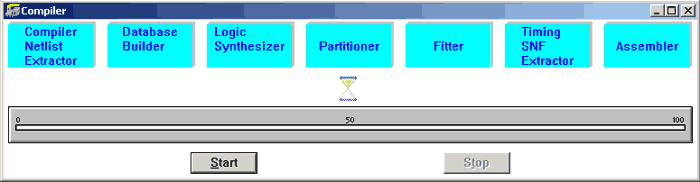

Затем нам надо скомпилировать схему. Выбираем:

MAX+plus II > Compiler

Вываливается окошко:

Жмем Start. Оно компилится. Если все правильно — компилятор говорит что все круто. Жмем ОК.

Все. Теперь можно составить график для симулятора. Для этого запускаем редактор графиков:

MAX+plus II > Waveform Editor

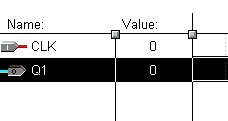

Два раза тыкаемся по пустому месту в графе Name или Value. Вываливается окно:

Нажимаем List — в окошке Nodes&Groups from SNF. Вываливается список всех выводов нашей схемы:

CLK (I)

Q1 (O).

Поставим сначала вход, то есть — CLK.

Выделяем его, жмем OK — и он оказывается на графике.

Точно так же вытащим теперь выход Q1.

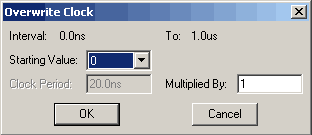

Теперь выделяем вход CLK и нажимаем слева на кнопочку

— «сгенерить тактовую частоту». Вывалится окно:

В нем нас спрашивают о начальном значении (Starting Value)

и о том, через сколько линий сетки изменяется состояние сигнала.

Сетка на графике обозначается серыми вертикальными пунктирными линиями.

Ничего не трогаем и жмем OK.

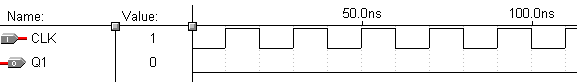

Вот что получилось:

Теперь самое время сохранить файл. Сохраняем под тем же именем, что и графический файл — counter.

Иначе ничего не получится.

Теперь идем:

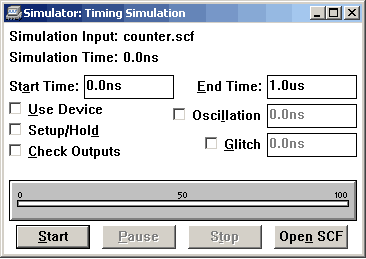

MAX+plus II > Simulator.

Жмем Start — симулятор быренько симулирует и говорит что все очень хорошо

(или все плохо, зависит от расположения звезд).

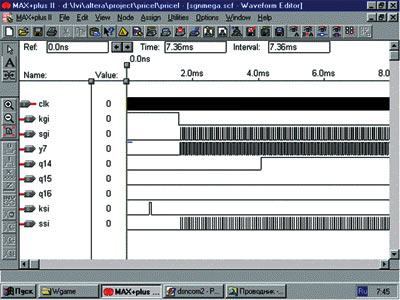

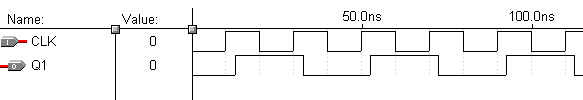

Смотрим в окошко редактора графиков (Waveform Editor). Что получилось:

Этот график наглядно демонстрирует работу счетного триггера:

по фронтам входного сигнала, состояние выхода изменяется на противоположное.

Как видите, момент изменения выхода отстает от фронта по входу примерно на 2,5 нс.

Это — нормально. Это — задержка на распространение сигнала.

Дело в том, что симулятор очень умный, и поэтому просчитывает даже такие «мелочи» как задержка.

Ну все! Радуемся. Идем на перекур.

В следующий раз мы составим схему ажно на четырех счетных триггерах и проверим ее работу на симуляторе.

<<—Вспомним пройденное—-Поехали дальше—>>

|

Как вам эта статья? |

Заработало ли это устройство у вас? |

САПР «MAX+plus II» представляет собой интегрированную среду для разработки цифровых устройств на базе программируемых логических интегральных схем (ПЛИС) фирмы «Альтера» и обеспечивает выполнение всех этапов, необходимых для выпуска готовых изделий:

-

- создание проектов устройств;

- синтез структур и трассировку внутренних связей ПЛИС;

- подготовку данных для программирования или конфигурирования ПЛИС (компиляцию);

- верификацию проектов (функциональное моделирование и временной анализ);

- программирование или конфигурирование ПЛИС.

Наиболее полное фирменное описание системы «MAX+plus II» содержится в документе «MAX+plus II Getting Started Manual» на сайте фирмы «Альтера», в который входит учебник («Tutorial»). На русском языке достаточно подробное описание системы «MAX+plus II» можно найти в работе [1]. В настоящей статье приводятся в минимальном объёме сведения, необходимые для начального освоения технологии разработки цифровых устройств на ПЛИС фирмы «Альтера». В качестве примера рассмотрен процесс разработки устройства управления 7-сегментным светодиодным индикатором.

В состав пакета «MAX+plus II» входят следующие связанные между собой приложения, реализующие все перечисленные выше этапы разработки цифровых устройств на ПЛИС фирмы «Альтера»:

Приложения для ввода проектов (редакторы проектов)

«Graphic Editor» – графический редактор, предназначенный для ввода проекта в виде схемы соединений символов элементов, извлекаемых из стандартных библиотек пакета либо из библиотеки пользователя.

«Waveform Editor» – редактор временных диаграмм (некоторые авторы называют это приложение сигнальным редактором), который выполняет двойную функцию: на этапе ввода обеспечивает ввод логики проекта в виде диаграмм (эпюр) состояний входов и выходов, а на этапе моделирования обеспечивает ввод диаграмм тестовых (эталонных) входных состояний моделируемого устройства и задание перечня тестируемых выходов.

«Text Editor» – текстовый редактор, предназначенный для создания и редактирования текстовых файлов, содержащих описание логики проекта на языке описания устройств AHDL (Altera Hardware Description Language) или на близких к нему языках типа VHDL, «Verilog». Для освоения языка AHDL можно рекомендовать [1, 2], а также статьи, опубликованные в ряде номеров журнала «Чипньюс» («ChipNews») в 2000 г.

«Symbol Editor» – символьный редактор, позволяющий редактировать существующие символы и создавать новые. Кстати, любой откомпилированный проект может быть свёрнут в символ, помещён в библиотеку символов и использован как элемент в любом другом проекте.

«Floorplan Editor» – редактор связей (поуровневый планировщик), который на плане расположения основных логических элементов позволяет вручную распределять выводы ПЛИС (закреплять выводы за конкретными входными и выходными сигналами) и перераспределять некоторые внутренние ресурсы ПЛИС.

Приложения «MAX+plus II Compiler»

Это приложения, входящие в пакет компилятора и предназначенные для синтеза структуры, трассировки связей, проверки корректности проекта и локализации ошибок, формирования файлов программирования или конфигурирования ПЛИС:

«Netlist Extractor» – приложение, обеспечивающее извлечение списка соединений из исходного файла представления проекта, созданного при вводе проекта.

«Database Builder» – приложение, предназначенное для построения базы данных проекта.

«Logic Synthesizer» – приложение, обеспечивающее проверку корректности проекта по формальным правилам и синтез оптимальной структуры проекта.

«Partitioner» – приложение, обеспечивающее разбиение проекта на части в тех случаях, когда ресурсов одного кристалла (микросхемы) недостаточно для реализации проекта.

«Fitter» – трассировщик внутренних связей, обеспечивающий реализацию синтезированной структуры.

«SNF Extractor» – приложение, обеспечивающее извлечение параметров проекта, необходимых для функционального моделирования и временного анализа.

Приложения для верификации проектов

«Simulator» – приложение, которое совместно с редактором временных диаграмм предназначено для функционального моделирования проекта с целью проверки правильности логики его функционирования.

«Timing Analyzer» – приложение, обеспечивающее расчет временных задержек от каждого входа до каждого логически связанного с ним выхода.

«MAX+plus II Programmer»

Наконец, для программирования или конфигурирования ПЛИС используется приложение «MAX+plus II Programmer».

Программирование и перепрограммирование микросхем, имеющих встроенную систему программирования (ISP), может осуществляться непосредственно в составе конечного изделия через специальный кабель, подключаемый либо к LPT-порту (Byte Blaster), либо к COM-порту (Bit Blaster) компьютера и технологического 10-контактного соединителя интерфейса JTAG, устанавливаемого на плате изделия. Схемы кабелей можно найти на сайте фирмы «Альтера». Если на плате изделия устанавливается несколько ПЛИС со встроенными системами программирования, то все они могут программироваться через один технологический разъём. Для этой цели приложение «Programmer» имеет режим «Multi-Device» (к сожалению, бесплатные версии пакета этот режим не поддерживают). Схемы подключения ПЛИС к интерфейсу JTAG приводятся в документации на «Bit Blaster» и «Byte Blaster». Для программирования остальных микросхем необходимо дополнительно использовать внешний программатор, который также может подключаться к COM- или LPT-порту.

Сервисные приложения

В состав САПР, кроме того, входят три сервисных приложения:

«Design Doctor» – приложение, предназначенное для проверки корректности проекта с использованием эмпирических правил.

«Message Processor» – процессор сообщений, обеспечивающий обработку, вывод на отображение и локализацию (указание места в проекте, к которому оно относится) сообщений трёх типов: сообщений об ошибках («Error»), предупреждений («Warning») и информационных сообщений («Info»). Причину вывода того или иного сообщения можно выяснить через опцию «Help on Message» процессора сообщений. При наличии сообщений об ошибках компиляция проекта невозможна до их полного устранения. При наличии предупреждений компиляция успешно завершается, однако наличие предупреждения свидетельствует об обнаружении проблемы, которая может привести к неверной работе устройства. Поэтому все предупреждения должны быть тщательно проанализированы с использованием «Help on Message», до выяснения причин их появления и последующего устранения этих причин (или игнорирования предупреждения, что иногда бывает возможно). Информационные сообщения нужно только принимать к сведению.

«Hierarhy Display» – приложение, обеспечивающее обзор иерархической структуры проекта, который может состоять из множества составленных в различных редакторах и свёрнутых в символы проектов более низких уровней, причём число уровней не ограничивается. Основной проект (проект самого верхнего уровня) должен быть создан в графическом редакторе (если проект имеет только один уровень иерархии, то он может быть создан в любом редакторе).

Рабочие каталоги системы

Во время инсталляции пакета создаются два каталога: каталог MAXPLUS2, который содержит все приложения и библиотеки пакета, и каталог MAX2WORK, который содержит подкаталог CHIPTRIP со всеми файлами учебного проекта, рассмотренного в руководстве («MAX+plus II Tutorial»), и ряд подкаталогов, используемых электронным справочником («MAX+plus II Help»). В этом же каталоге MAX2WORK следует размещать и рабочие каталоги создаваемых проектов устройств.

Необходимость создания отдельных каталогов для каждого разрабатываемого проекта обусловлена тем, что в процессе разработки проекта системой MAX+plus II создаётся и поддерживается множество файлов, относящихся к текущему проекту. Прежде всего это файл проекта («Project File»), название которого определяет название проекта в целом. Этот файл содержит основную логику и иерархию проекта, обрабатываемую компилятором. Кроме того, создаётся ряд вспомогательных файлов, связанных с проектом, но не являющихся частью логики проекта. Большая часть вспомогательных файлов создаётся и автоматически помещается в каталог проекта в процессе ввода и компиляции проекта. Это прежде всего файлы назначений и конфигурации (.ACF), файлы отчётов (.RPT), файлы данных для функционального моделирования и временного анализа (.SNF), файлы данных для программирования (.POF) и ряд других. Названия этих файлов всегда совпадают с названием проекта. Некоторые вспомогательные файлы создаются пользователем: например, для выполнения функционального моделирования создаётся файл (.SCF), содержащий описание начальных и текущих состояний входных сигналов (входов) и перечень выходов, для которых должны быть определены выходные сигналы. Поэтому перед началом работы над новым проектом следует создать рабочий каталог проекта, при этом имя каталога можно выбирать произвольно (т.е. имя каталога может не совпадать с именем файла проекта).

Начало работы

После запуска пакета открывается главное окно. В самой верхней строке содержится имя последнего проекта, с которым велась работа. Две следующие строки являются обычными для виндоуз-приложений: строка основного меню и панель инструментов, в левой части которой расположены стандартные функции «Виндоуз» («New», «Open», «Save», «Print», «Cut», «Copy», «Paste», «Undo»), а в правой части – специфические инструменты пакета, с помощью которых осуществляется запуск его основных приложений. Назначение любого инструмента можно узнать, совместив с ним указатель мыши, при этом в строке подсказки (самая нижняя строка окна) появляется текст с пояснением. Для запуска приложений можно использовать также пункты меню «MAX+plus II» (в основном меню).

Рис. 1. Основная часть главного окна системы «MAX+plus II»

Порядок использования основных приложений системы «MAX+plus II» рассмотрим на примере разработки устройства индикации двоичных данных в шестнадцатеричной форме на 2-разрядном 7-сегментном светодиодном индикаторе для гипотетической микропроцессорной системы с 8-разрядной шиной данных и 16-разрядной шиной адреса. Для определённости будем считать, что порт индикации имеет адрес 10h, а в качестве индикатора используется индикатор типа DA-56 с общим анодом, т.е. сигналы управления сегментами должны иметь активные низкие уровни для подсветки сегментов, соответствующих шестнадцатеричному представлению входного двоичного кода.

Основными элементами такого устройства являются:

- схема формирования сигнала записи в порт, включающая 16-разрядный адресный селектор и схему стробирования сигнала записи;

- 8-разрядный регистр порта;

- комбинационные схемы преобразования двоичных кодов тетрад в сигналы управления сегментами индикатора (нагрузочная способность ПЛИС фирмы «Альтера» позволяет подключать светодиоды непосредственно к выводам микросхем через нагрузочные сопротивления номиналом 330…390 Ом).

В разрабатываемый проект целесообразно включить два уровня иерархии:

- уровень структурных элементов, в который входит схема формирования сигнала записи в порт и комбинационные схемы преобразования двоичных кодов тетрад в сигналы управления сегментами индикатора;

- уровень проекта в целом.

Для начала, используя стандартные средства «Виндоуз», создадим в каталоге MAX2WORK рабочий каталог под именем MOD_IND. Затем создадим проект схемы формирования сигнала записи в порт. Будем создавать его в графическом редакторе. Для этого запускаем систему «MAX+plus II» и создаём новый файл (крайний левый значок панели инструментов). В открывшемся диалоговом окне «New» выбираем пункт «Graphic Editor file» и нажимаем кнопку «ОК», при этом автоматически открывается окно графического редактора.

Рис. 2. Окно графического редактора «Graphic Editor»

Окно редактора имеет ряд дополнительных пунктов основного меню и панель инструментов редактора, расположенную вертикально с левой стороны окна. Сохраним новый файл проекта (через меню «File > Save») под именем WRITE_PORT (расширение будет присвоено автоматически) в созданном каталоге MOD_IND. Имя файла проекта следует обязательно привязать к имени проекта – это делается при выборе пункта «Set Project to Current File» (в подменю «Project» меню «File» главного меню рабочего окна).

Для создания графического проекта можно использовать библиотеки примитивов (MAXPLUSMAX2LIBPRIM), макрофункций (MAXPLUSMAX2LIBMF) и параметризированных мегафункций (MAXPLUSMAX2LIBMEGA_LPM).

Примитивы включают большой набор основных логических элементов, триггеров, элементов входа и выхода (INPUT, OUTPUT, BIDIR), а также вспомогательные элементы: GND (логический ноль), VCC (логическая единица).

Макрофункции включают главным образом эквиваленты логических микросхем 74-й серии.

Параметризированные мегафункции позволяют реализовывать многовходовые и многоразрядные элементы цифровой схемотехники (логику, регистры, мультиплексоры и т.д.), вводя ряд параметров в специально обозначенных областях условных графических обозначений этих элементов. Порядок использования мегафункций можно найти в соответствующем разделе электронного справочника системы («Help»), а также в документе «LPM Quick Reference Guide» на CD-ROM, прилагаемом к [2].

Работа в графическом редакторе

Прежде чем перейти непосредственно к созданию проекта схемы формирования сигнала записи в порт, рассмотрим некоторые особенности и свойства графического редактора системы «MAX+plus II».

Рис. 3. Диалоговое окно размещения элементов

Для размещения элементов в окне редактора используется диалоговое окно «Enter Symbol», которое можно открыть через меню «Symbol» основного меню редактора (пункт «Enter Symbol»). Однако удобнее вызывать это окно двойным щелчком левой клавиши мыши по свободному пространству открытого окна редактора, после чего выбранный элемент будет размещён именно в этом месте (позиционирование элемента производится по верхнему левому углу условного обозначения элемента). Выбрать и установить необходимый элемент можно двумя способами:

- Набрать имя элемента (примитива, мега- или макрофункции) в окне «Symbol Name» диалогового окна «Enter Symbol» и нажать «ОК».

- Выбрать необходимую библиотеку в окне «Symbol Libraries» диалогового окна «Enter Symbol» и двойным щелчком левой клавиши мыши открыть её. Затем аналогичным образом выбрать необходимый элемент в окне «Symbol File».

Установленный элемент можно переместить в другое место обычным приёмом «Drag&Drop». Перемещение элементов может производиться без сохранения или с сохранением соединений, проведённых между элементами, в зависимости от состояния On/Оff кнопок «Rubberbanding Functions», расположенных в нижней части панели инструментов редактора.

Выводы символов элементов можно соединить сигнальными линиями или присваиваемыми одинаковыми именами. Для проведения сигнальной линии необходимо совместить указатель курсора (конец стрелки) с выводом элемента, при этом курсор автоматически превращается в инструмент рисования ортогональных линий (перекрестие). После этого проводится необходимая линия (при нажатой и удерживаемой левой кнопке мыши). За один приём можно провести два ортогональных отрезка. Если этого недостаточно, то процедуру можно повторять, начиная с конца проведённой линии или с вывода другого элемента.

Для соединения элементов необязательно проводить сплошные соединительные линии между выводами. Достаточно выводам, которые должны быть соединены между собой, присвоить одинаковые имена. Поименованный вывод элемента называется узлом («Node»). Для присвоения узлу имени необходимо сначала провести короткую сигнальную линию. Так как по окончании рисования линии она остаётся выделенной (выделенные элементы обозначаются красным цветом или красной рамкой), то имя узла можно вводить сразу. Если линия не выделена (имеет чёрный цвет), то необходимо выделить её щелчком левой кнопки мыши в том месте, где должно начинаться имя узла, и набрать на клавиатуре требуемое имя.

Установленные элементы и группы элементов (любую выделенную область окна) можно удалять, перемещать, поворачивать, копировать и размножать в пределах окна редактора, а также переносить в другие окна через буфер обмена. Все эти операции можно выполнять с использованием пунктов меню «Edit» (в основном меню редактора), предварительно выделив требуемую область или элемент.

Выделение отдельных элементов, включая и соединительные линии, производится щелчком левой кнопки мыши на изображении символа элемента. Выделение области возможно при нажатой и удерживаемой левой кнопке мыши. Выделенная область обозначается рамкой чёрного цвета, а все выделенные элементы – красным цветом.

Для удаления, копирования, вырезания, поворота и некоторых других операций с элементами можно использовать выпадающее контекстное меню, которое вызывается щелчком правой кнопки мыши по выбранному элементу. Для перемещения выделенных областей в пределах окна используется способ «Drag&Drop», а для размножения выделенных областей и элементов – «Drag&Drop» при нажатой и удерживаемой клавише CTRL.

Часть инструментов редактора, расположенных на вертикальной панели с левой стороны окна, предназначена для созданий поясняющих надписей, рисунков и таблиц, которые не являются частью проекта и не обрабатываются компилятором.

Этап 1: создание схемы проекта

Создание схемы проекта целесообразно начинать с размещения узлов входов и выходов и присвоения этим узлам имён. В нашем случае необходимо разместить входы адресных линий A0…A15, вход сигнала записи /WR (низкий активный уровень) и один выход сигнала записи в порт WR_PORT. Используем для этой цели библиотеку примитивов, которая содержит примитивы INPUT (для входов) и OUTPUT (для выходов). Каждому вводу должно быть присвоено своё имя. Для этого необходимо дважды щёлкнуть мышью на поле (входа/выхода), в появившемся чёрном прямоугольнике набрать новое имя и нажать клавишу ENTER. Переход к набору имени следующего элемента ввода может осуществляться по нажатию клавиши ENTER.

Логика разрабатываемого проекта также может быть реализована с использованием примитивов: двух элементов OR8 (8-входовый элемент «ИЛИ»), одного элемента NOR3 (3-входовый элемент «ИЛИ-НЕ») и одного инвертора NOT. В описанном выше порядке размещаем требуемые элементы и выполняем необходимые соединения.

Рис. 4. Готовый проект устройства формирования сигнала записи в порт

Заметим, что предложенный вариант реализации логики устройства – не единственный и не самый лучший. Заинтересованный читатель может реализовать этот проект с использованием языка AHDL (самый предпочтительный вариант) или мегафункции LPM_OR.

Этап 2: компиляция и создание символа проекта

Следующий этап – компиляция и создание символа проекта для включения его в файл проекта верхнего уровня. Перед компиляцией можно выполнить проверку корректности введённого проекта. Проверка осуществляется через подменю «Project» (меню «File» главного меню рабочего окна) путём выбора пункта «Save&Check» или щелчком левой кнопки мыши на пиктограмме соответствующего инструмента основной панели инструментов.

Компиляция осуществляется также через подменю «Project» путём выбора пункта «Save&Compile» или опять же с помощью соответствующего инструмента основной панели инструментов.

Рис. 5. Вид окна компилятора после успешного завершения компиляции

По результатам компиляции процессор сообщений проинформирует нас о том, что для реализации данного проекта могут быть использованы ПЛИС семейства «MAX3000A», а именно ПЛИС типа «EPM 3032ALC44» (в корпусе PLCC с 44 выводами).

Создание символа проекта осуществляется через подменю «Project», в котором следует выбрать пункт «Create Default Symbol» – этот пункт становится доступным только после закрытия окна компилятора. Созданный символ будет помещён в каталог проекта. Использование созданных символов, так же как и элементов других библиотек, производится через диалоговое окно «Enter Symbol».

Этап 3. Создание проекта и символа комбинационной схемы

Следующий шаг – создание проекта и символа комбинационной схемы преобразования двоичного кода тетрады в сигналы управления сегментами индикатора.

Таблица 1

Перечень состояний комбинационной схемы преобразования двоичного кода тетрады

| Состояния входов1 | HEХ-код | Состояния выходов2 | |||||||||

| In3 | In2 | In1 | In0 | /a | /b | /c | /d | /e | /f | /g | |

| 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 1 |

| 0 | 0 | 0 | 1 | 1 | 1 | 0 | 0 | 1 | 1 | 1 | 1 |

| 0 | 0 | 1 | 0 | 2 | 0 | 0 | 1 | 0 | 0 | 1 | 0 |

| 0 | 0 | 1 | 1 | 3 | 0 | 0 | 0 | 0 | 1 | 1 | 0 |

| 0 | 1 | 0 | 0 | 4 | 1 | 0 | 0 | 1 | 1 | 0 | 0 |

| 0 | 1 | 0 | 1 | 5 | 0 | 1 | 0 | 0 | 1 | 0 | 0 |

| 0 | 1 | 1 | 0 | 6 | 0 | 1 | 0 | 0 | 0 | 0 | 0 |

| 0 | 1 | 1 | 1 | 7 | 0 | 0 | 0 | 1 | 1 | 1 | 1 |

| 1 | 0 | 0 | 0 | 8 | 0 | 0 | 0 | 0 | 0 | 0 | 0 |

| 1 | 0 | 0 | 1 | 9 | 0 | 0 | 0 | 0 | 1 | 0 | 0 |

| 1 | 0 | 1 | 0 | A | 0 | 0 | 0 | 1 | 0 | 0 | 0 |

| 1 | 0 | 1 | 1 | B | 1 | 1 | 0 | 0 | 0 | 0 | 0 |

| 1 | 1 | 0 | 0 | C | 0 | 1 | 1 | 0 | 0 | 0 | 1 |

| 1 | 1 | 0 | 1 | D | 1 | 0 | 0 | 0 | 0 | 1 | 0 |

| 1 | 1 | 1 | 0 | E | 0 | 1 | 1 | 0 | 0 | 0 | 0 |

| 1 | 1 | 1 | 1 | F | 0 | 1 | 1 | 1 | 0 | 0 | 0 |

1 Приведены все возможные состояния входов, соответствующие значениям двоичного кода.

2 Приведены состояния выходных сигналов управления сегментами индикатора, обеспечивающие отображение символов шестнадцатеричного кода (значения кода см. в отдельной колонке).

Для создания проекта этого устройства используем редактор временных диаграмм («Waveform Editor»). Для этого следует нажать кнопку открытия нового файла на панели инструментов, в открывшемся диалоговом окне «New» отметить пункт «Waveform Editor file», в соседнем окне выбрать расширение .WDF (расширение .SCF используется для моделирования) и нажать «ОК», после чего открывается окно редактора.

Окно редактора имеет четыре поля, разделённых вертикальными линиями. Первое поле слева («Name») предназначено для ввода имени узла, во втором поле («Type») отображается тип ввода (INPUT, OUTPUT, BIDIR), в третьем поле («Value») показаны состояния выводов, соответствующие положению специальной вертикальной визирной линии, которая при открытии окна установлена в начало горизонтальной оси, размеченной в единицах времени.

Для перемещения визира в нужное место необходимо совместить курсор с вершиной визира (при этом курсор примет крестообразную форму) и при нажатой левой кнопке мыши перетащить визир в нужное место.

Четвёртое поле предназначено для задания требуемых состояний выводов, при этом используются инструменты с панели инструментов редактора, которая расположена вертикально вдоль левой стороны окна. Активизация панели инструментов происходит только в том случае, если выделен один из узлов. Чтобы выделить узел, необходимо щёлкнуть левой кнопкой мыши на имени узла, можно также выделить любой участок вдоль горизонтальной оси, при этом границы выделяемых участков привязываются к сетке.

Параметры сетки устанавливаются следующим образом: с помощью пункта «End Time» (меню «File») задаётся максимальное значение временного интервала с указанием единиц измерения, а с помощью пункта «Grid Size» (меню «Options») – шаг сетки. В верхней части экрана расположены окна для точного отсчёта интервалов времени.

Сохраним созданный файл в каталоге MOD_IND под именем CONV_BIN_HEX и присвоим проекту имя созданного файла (через подменю «Project» меню «File» главного меню рабочего окна, путём выбора пункта «Set Project to Current File»).

Для ввода имени узла можно использовать пункт «Insert Mode» меню «Node».

Рис. 6. Диалоговое окно пункта «Insert Mode»

В верхнее поле «Node Name» необходимо ввести имя узла, в окне «I/O Type» указать тип вывода и нажать «ОК». Кроме того, имена узлов можно вводить другим способом. Для этого необходимо щёлкнуть левой кнопкой мыши в поле «Name», при этом автоматически открывается диалоговое окно «Insert Mode».

Размещённые узлы можно редактировать, перемещать, удалять, размножать (с обязательным редактированием имени или типа, если это необходимо). Для редактирования используется то же диалоговое окно «Insert Mode». Остальные операции осуществляются аналогично тому, как это делается в графическом редакторе.

В нашем случае (см. табл. 1) необходимо задать 16 возможных состояний 4-х входов и состояния 7-ми выходов, соответствующие каждому состоянию входов. Для этого вся горизонтальная ось должна быть разбита на 16 дискрет. Например, установив значение «End Time» 160 нс, а «Grid Size» – 10 нс, получим 16 дискрет с шагом сетки 10 нс. После этого последовательно выделяем узлы и дискреты и с помощью панели инструментов задаём требуемые состояния входов и выходов.

Рис. 7. Введённый файл проекта примера

Далее компилируем файл и создаём символ этого устройства, как описано выше.

После этого в графическом редакторе создаем и компилируем файл проекта всего устройства в целом. В качестве регистра порта используем макрофункцию 74374, а в качестве остальных элементов – элемент WRITE_PORT и два элемента CONV_BIN_HEX.

Порядок открытия, создания и компиляции файла проекта верхнего уровня ничем не отличается от порядка создания и компиляции файла WRITE_PORT, который был рассмотрен выше.

Рис. 8. Схема описанного в примере проекта устройства индикации

Назначение типа ПЛИС и выводов ПЛИС

Тип ПЛИС, необходимый для реализации проекта, может быть выбран автоматически или назначен вручную. При создании файла проекта по умолчанию установлен режим автоматического выбора минимальной по объёму ПЛИС, в которой может быть реализован данный проект. При необходимости тип ПЛИС может быть назначен вручную с помощью пункта «Device» (меню «Assign» основного меню системы). После назначения устройства проект необходимо перекомпилировать.

Выводы ПЛИС также первоначально назначаются автоматически. После завершения работы над проектом необходимо закрепить или переназначить выводы ПЛИС, для того чтобы при возможной последующей доработке (отладке) проекта в составе всего изделия компилятор не мог изменить их назначение. Эта операция выполняется с помощью редактора «Floorplan Editor», который запускается либо через меню «MAX+plus II» (в основном меню), либо через панель инструментов.

Рис. 9. Окно редактора связей «Floorplan Editor» (при установленном режиме отображения текущих назначений выводов)

С левой стороны окна имеется панель инструментов, среди которых имеется две кнопки: одна из них устанавливает режим отображения результатов компиляции (…last compilation), вторая – режим отображения текущих назначений выводов (…current assignments). Напомним, что назначение кнопок панелей инструментов поясняется в строке подсказки в нижней части окна.

Для назначения или закрепления выводов необходимо мышью перетащить имена выводов, отображаемых в окне «Unassigned Nodes&Pins», на соответствующие номера выводов ПЛИС, а затем перекомпилировать проект. После этого любые изменения, вносимые во внутреннюю структуру проекта, т.е. не связанные с добавлением или удалением выводов, не будут изменять назначение выводов. Заметим, что ПЛИС семейства «MAX 7000S» (а также некоторые другие) имеют встроенную систему программирования ISP, которая использует четыре вывода: #TDI, #TDO, #TMS и #TSK. Эти выводы не должны использоваться для других целей.

Завершение работы

Все результаты работы над проектом фиксируются в файле с расширением .RPT, который представляет собой обычный текстовый файл и содержит подробное описание реализованного проекта, в том числе и описание назначения выводов, необходимое для разработки принципиальной схемы целевого устройства. Файл .RPT можно открыть через меню «File» или нажатием соответствующей кнопки на панели инструментов.

Для завершения работы над проектом необходимо провести функциональное моделирование. Для этого необходимо создать исходный файл с расширением .SCF, задать тестовые (эталонные) состояния входов, выбрать проверяемые выходы и запустить «Simulator».

Для создания исходного файла необходимо открыть новый файл, в диалоговом окне «New» отметить пункт «Waveform Editor file», установить в соседнем поле окна расширение .SCF и нажать «ОК», а затем сохранить его через меню «File» основного меню. После этого необходимо связать файл с проектом. Для этого необходимо войти в меню «Node» и выбрать пункт «Enter Nodes from SNF».

Рис. 10. Диалоговое окно «Enter Nodes from SNF»

После нажатия кнопки «List» в левой панели диалогового окна «Enter Nodes from SNF» появляется список доступных узлов («Available Nodes&Groups»), выделенный синим цветом, который необходимо перенести на правую панель («Selected Nodes&Groups»), для чего необходимо нажать кнопку со стрелкой, расположенную между панелями. После нажатия кнопки «ОК» в окне редактора появляется готовый шаблон (заготовка) для задания тестовых состояний входов.

Перед началом ввода тестовых состояний необходимо в порядке, описанном выше, задать длительность интервала моделирования и установить шаг сетки с учётом временных параметров реальных сигналов, которые будут подаваться на вход ПЛИС в целевом устройстве.

Сами тестовые состояния входов вводятся так же, как и при создании проекта (см. выше). В данном случае моделируется процесс записи двоичного кода 01010101 по адресу 10h.

Рис. 11. Фрагмент исходного файла для моделирования разработанного устройства с заданными состояниями входов

«Simulator» может быть запущен либо через меню «MAX+plus II» (в основном меню), либо через панель инструментов, при этом открывается диалоговое окно с кнопками «Start» и «Open SCF». Для начала моделирования необходимо нажать кнопку «Start», а для просмотра результатов – «Open SCF».

Рис. 12. Фрагмент файла с результатами функционального моделирования

Для определения временных соотношений используется приложение «Timing Analyzer», которое запускается так же, как «Simulator». Результаты расчёта временных задержек отображаются в виде таблицы «Delay Matrix»

Рис. 13. Фрагмент таблицы «Delay Matrix»

В заключение ещё раз подчеркнём, что рассмотренный пример является одним из самых простых и иллюстрирует только некоторые приёмы и возможности работы с САПР «MAX+plus II». Вместе с тем надеемся, что приведённый пример достаточно хорошо иллюстрирует эффективность системы «MAX+plus II» и способен стимулировать стремление заинтересованных специалистов к более глубокому изучению, освоению и использованию этого инструмента в их практической работе. Желаем творческих успехов!

Автор: Владимир Поречный

Литература

Стешенко В.Б. ПЛИС фирмы ALTERA: Проектирование устройств обработки сигналов. – М.: Додэка, 2000.

Антонов А.П. Язык описания цифровых устройств AlteraHDL: Практический курс. – М.: ИП «Радиософт», 2001. – К книге прилагается CD-ROM, содержащий САПР «MAX+PLUS II».

Лекция 14 – Система проектирования MAX+PLUS II для ПЛИС фирмы Altera

Общие сведения. Лекции 14-17 посвящены системе MAX+PLUS II для ПЛИС фирмы Altera. Все пакеты работают на платформе IBM PC. Для нормальной инсталляции и работы САПР MAX+PLUS II (версия 9.4 вышла в декабре 1999 года) необходима IBM PC-совместимая ЭВМ с процессором не хуже Pentium, объёмом ОЗУ не хуже 16 Мб и свободным местом на жёстком диске порядка 150-400 Мб.

Каталоги системы MAX+PLUS II. Во время инсталляции системы MAX+PLUS II создаются два каталога: maxplus2 и max2work. Каталог maxplus2 содержит системное ПО и файлы данных, и разбит на подкаталоги, перечисленные в таблице 14.1. Каталог max2work содержит файлы обучающей программы и примеры, и подразделяется на подкаталоги, описанные в таблице 14.2.

Таблица 14.1 – Структура системного каталога maxplus2

Таблица 14.2 – Структура рабочего каталога max2work

|

Подкаталог |

Описание |

|

.ahdl |

содержит файлы примеров, иллюстрирующих тему «Как использовать язык AHDL” (Hou to Use AHDL) в электронном справочнике (MAX+PLUS II Help) и в руководстве MAX+PLUS II AHDL |

|

.chiptrip |

содержит все файлы обучающего проекта chiptrip, описанного в руководстве |

|

.edif |

содержит все файлы примеров, иллюстрирующих особенности EDIF в электронном справочнике |

|

.tutorial |

содержит информационный файл read.me обучающего проекта chiptrip |

Продолжение таблицы 14.2

|

Подкаталог |

Описание |

|

.vhdl |

содержит файлы примеров, иллюстрирующих тему «Как использовать язык VHDL» в электронном справочнике и в руководстве |

|

.verilog |

содержит файлы примеров, иллюстрирующих тему «Как использовать язык верификационного протокола HDL» в электронном справочнике и в руководстве |

Название системы MAX+PLUS II является аббревиатурой от Multiple Array MatriX Programmable Logic User System (Пользовательская система программирования логики упорядочных структур). Система MAX+PLUS II разработана фирмой Altera и обеспечивает многоплатформенную архитектурно-независимую среду создания дизайна, легко приспосабливаемую для конкретных требований пользователя. Система MAX+PLUS II имеет средства удобного ввода дизайна, быстрого прогона и непосредственного программирования устройства.

Состав ПО системы MAX+PLUS II. Представленный на рисунке 14.1 состав ПО системы MAX+PLUS II является полным комплектом, обеспечивающих создание логических дизайнов для устройств фирмы Altera с программируемой логикой, в том числе семейства устройства Classic, MAX 5000, MAX 7000, MAX 9000, FLEX 6000, FLEX 8000, и FLEX 10K. Информация о других поддерживаемых семействах устройств фирмы Altera приведена в файле read.me в системе MAX+PLUS II.

Рисунок 14.1 – Среда проектирования в системе MAX+PLUS II

Система MAX+PLUS II предлагает полный спектр возможностей логического дизайна:

1. разнообразные средства описания проектов с иерархической структурой,

2. мощный логический синтез,

3. компиляцию с заданными временными параметрами,

4. разделение на части,

5. функциональное и временное тестирование (симуляцию),

6. тестирование нескольких связанных устройств,

7. анализ временных параметров системы,

8. автоматическую локализацию ошибок,

9. программирование,

10. верификация устройств.

В системе MAX+PLUS II можно как читать, так и записывать файлы на

языке AHDL и файлы трассировки в формате EDIF, файлы на языках описания аппаратуры Verilog HDL и VHDL, а также схемные файлы OrCAD. Кроме того, система MAX+PLUS II читает файлы трассировки, созданные с помощью ПО Xilinx, и записывает файлы задержек в формате SDF для удобства взаимодействия с пакетами, работающими с другими промышленными стандартами.

Приложения в системе MAX+PLUS II. Система предлагает пользователю богатый графический интерфейс, дополненный иллюстрированной оперативной справочной системой. В полную систему MAX+PLUS II входят несколько внедрённых в систему приложений (см. рисунок 14.2). Совокупность иерархически связанных файлов проекта Design file называется проектом (project).

Рисунок 14.2 – Приложения в системе MAX+PLUS II

Возможно описание проекта Design Entry в виде файла на языке описания аппаратуры, созданного либо во внешнем редакторе, либо в текстовом редакторе MAX+PLUS II (Text Editor), в виде схемы электрической принципиальной c помощью графического редактора Graphic Editor, в виде временной диаграммы, созданной в сигнальном редакторе Waveform Editor. Для удобства работы со сложными иерархическими проектами каждому поддизайну может быть сопоставлен символ, редактирование которого производится с помощью графического редактора Symbol Editor. Размещение узлов по логическим блокам и выводам ПЛИС выполняют с помощью поуровневого планировщика Floorplan Editor.

Верификация проекта (Project verification) выполняется с помощью симулятора (simulator), результаты работы которого удобно просмотреть в сигнальном редакторе Waveform Editor. Тестовые воздействия создаются также в сигнальном редакторе.

Компиляция проекта, включая извлечение списка соединений (Netlist Extractor), построение базы данных проекта (Data Base Builder), логический синтез (logic synthesis), извлечение временных, функциональных параметров проекта (SNF Extractor), разбиение на части (Partioner), трассировка (Filter) и формирование файла программирования или загрузки (Assembler), выполняются с помощью компилятора системы (Compiler). Непосредственно программирование или загрузка конфигурации устройств с использованием соответствующего аппаратного обеспечения выполняется с использованием модуля программатора (Programmer).

Многие команды – такие, как открытие файлов, ввод назначений устройств, выводов и логических элементов, компиляция текущего проекта – похожи для многих приложений системы MAX+PLUS II. Редакторы для разработки проекта (графический, текстовый и сигнальный) имеют много общего со вспомогательными редакторами (поуровневого планирования и символьный). Каждый редактор разработки проекта позволяет выполнять похожие задачи (например, поиск сигнала или символа) похожим способом. Можно легко комбинировать разные типы файлов проекта в иерархическом проекте, выбирая для каждого функционального блока тот формат описания проекта, который больше подходит. Поставляемая фирмой Altera большая библиотека мега- и макрофункций, в том числе функции из библиотеки параметризованных моделей (LPM), обеспечивает широкие возможности ввода дизайна.

Можно одновременно работать с разными приложениями MAX+PLUS II. Например, можно открыть несколько файлов проекта и переносить информацию из одного в другой в процессе компиляции или тестирования другого проекта. Или, например, просматривать всё дерево проекта и в окне просмотра перемещаться с одного уровня на другой, а в окне редактора будет появляться выбранный вами файл, причём вызывается автоматически соответствующий редактор для каждого файла.

Разработка проекта в системе MAX+PLUS II. Этапы проектирования. Процедура разработки нового проекта состоит из следующих этапов:

· создание нового файла (design file) проекта или иерархической структуры нескольких файлов проекта с использованием различных редакторов;

· задание имени файла проекта верхнего уровня (Top of hierarchy);

· назначение семейства ПЛИС для реализации проекта;

· открытие окна компилятора (Compiler) и его запуск. Можно подключить модуль извлечения временных задержек Timing SNF Extractor для создания файла разводки, используемого при тестировании временных параметров;

· при успешной компиляции возможно тестирование и временной анализ;

· программирование выполняется путём загрузки модуля программатора (Programmer) с последующей вставкой устройства в программирующий адаптер программатора MPU (Master Programming Unit) или с помощью подключения устройства Master Blaster или кабеля загрузки к устройству, программируемому в системе:

· выбор кнопки Program для программирования устройств с памятью типа EPROM или EEPROM либо выбор кнопки Configure для загрузки конфигурации устройства с памятью типа SRAM.

MAX+PLUS II запускается двумя способами: щелкнув дважды левой кнопкой мыши на пиктограмме MAX+PLUS II или набрав maxplus2 в командной строке. При этом автоматически открывается Главное окно, охватывающее все приложения системы. В верхней части окна отображается имя проекта и те-

|

Рисунок 14.3 – Окно меню MAX+PLUS II |

кущего файла. Затем следует строка меню, под ней панель основных инструментов системы, обеспечивающая быстрый вызов её компонентов. В нижней части экрана располагается строка подсказки. Вызов компонентов системы удобно производить через окно меню MAX+PLUS II, представленном на рисунке 14.3. Программное обеспечение (ПО) системы MAX+PLUS II содержит 11 приложений и главную управляющую оболочку. Различные приложения могут быть активизированы мгновенно, что позволяет пользователю переключаться между ними щелчком мыши или с помощью команд меню. Приложения системы MAX+PLUS II. В таблице 14.3 приведено описание приложений. Следует понять разницу между файлами проекта и вспомогательными файлами. Файл проекта – это графический, текстовой |

или сигнальный файл. Этот файл содержит логику для проекта MAX+PLUS II и обрабатывается компилятором. Вспомогательные файлы – это файлы, связанные с проектом MAX+PLUS II, но не являющиеся частью иерархического дерева проекта. Примерами вспомогательных файлов являются файлы назначений и конфигурации, символьные файлы, файлы отчётов и файлы тестовых векторов.

Проект состоит из всех файлов иерархической структуры дизайна, в том числе вспомогательных и выходных файлов. В системе MAX+PLUS II легко доступны все инструменты для создания логического проекта. Разработка проекта ускоряется за счёт имеющихся стандартных логических функций, в том числе примитивов, мегафункций, библиотеки параметризированных модулей LPM. Крайне вредно использовать устаревшие библиотеки и переносить на ПЛИС схемотехнику стандартных ТТЛ серий. Следует разработать проект именно под архитектуру ПЛИС для получения более или менее разумных результатов.

Таблица 14.3 – Приложения системы MAX+PLUS II

|

Прил-ние |

Выполняемая функция |

|

Hierarchy Display |

Обзор иерархии — отображает иерархическую структуру файлов в виде дерева с ветвями |

|

Graphic Editor |

Графический редактор –разрабатывает схемный логический дизайн. Примитивы, мегафункции фирмы Altera используются в качестве основных блоков |

|

Symbol Editor |

Символьный редактор –редактирует существующие символы и создаёт новые |

|

Text Editor |

Текстовый редактор –создаёт и редактирует текстовые файлы, написанные на языках описания AHDL, VHDL и Verilog HDL |

|

Waveform Editor |

Сигнальный редактор – выполняет двойную функцию; это инструмент для разработки дизайна и инструмент для ввода тестовых сигналов и наблюдения результатов тестирования. |

|

Floorplan Editor |

Поуровневый планировщик –графическими средствами даёт назначения выводам устройства и ресурсам логических элементов и блоков. |

|

Compiler |

Компилятор – обрабатывает логические проекты, разработанные для семейств устройств Altera |

|

Simulator |

Симулятор – тестирует логические операции и внутреннюю синхронизацию проектируемой логической схемы. Возможны три режима тестирования: функциональное, временное и тестирование нескольких соединённых между собой устройств |

|

Timing Analyzer |

Анализатор временных параметров – анализирует работу проектируемой логической цепи после того, как она была синтезирована и оптимизирована компилятором, позволяет оценить возникающие задержки |

|

Program—mer |

Программатор –программирует, конфигурирует, проводит верификацию и испытывает устройства фирмы Altera |

|

Message Processor |

Генератор сообщений – выдаёт на экран сообщения об ошибках, предупреждающие и информационные сообщения о состоянии проекта |

Схемные файлы проекта создаются в графическом редакторе MAX+PLUS II. Можно также открыть, редактировать и сохранять схемы, созданные схемным редактором OrCAD.

Проекты на языках AHDL, VHDL и Verilog HDL создаются в текстовом редакторе MAX+PLUS II или любом другом текстовом редакторе.

|

Рисунок 14.4 – Меню назначений проекта Assign |

Сигнальные проекты создаются в сигнальном редакторе MAX+PLUS II. Файлы формата Xilinx, разработанные другими стандартными инструментами системы EDA, могут быть импортированы в среду MAX+PLUS II. Назначения параметров проекта. Во всех приложениях MAX+ PLUS II есть возможность с помощью команд из меню Assign (Назначить) вводить, редактировать и удалять типы назначений ресурсов, устройств и параметров, которые управляют компиляцией проекта, в том числе логическим синтезом, разделением на части и подгонкой. На рисунке 14.4 представлены команды меню Assign. Следующие функции являются |

общими для всех приложений MAX+PLUS II: назначения устройства, ресурсов и зондов; сохранение предыдущей версии; глобальные опции устройства в проекте; глобальные параметры проекта; глобальные требования к временным параметрам проекта; глобальный логический синтез проекта.

Ресурс является частью устройства фирмы Altera, как, например, контакт или логический элемент, который выполняет конкретные, определённое пользователем задание. Управление компиляцией проекта и его временными параметрами осуществляется с помощью различных назначений (Assign). Существуют следующие типы назначений.

Clique assignment (назначение клики) задаёт, какие логические функции должны оставаться вместе. Группировка логических функций в клики гарантирует, что они реализуются в одном и том же блоке логической структуры, блоке ячеек памяти, в одном ряду или устройстве. Узлы, объединённые в клики, при компиляции будут размещаться в пределах одного ЛБ.

Chip assignment (назначение чипа) задаёт, какие логические функции должны быть реализованы в одном и том же устройстве в случае разделения проекта на части (на несколько устройств).

Pin assignment (назначение вывода) назначает вход или выход одной логической функции, такой, как примитив или мегафункция, конкретному контакту или вертикальному (горизонтальному) ряду выводу ПЛИС.

Location assignment (назначение ячейки) задаёт расположение логической функции (узла). Назначения вывода, чипа и ячейки выполняется с помощью команды Assign/Pin/Location/Chip.. В поле данного окна можно выдать номер вывода (Pin), логическую ячейку или блок, а также, используя кнопки Change и Delete, изменить назначения.

Probe assignment (назначение зонда) присваивает легко запоминаемое уникальное имя входу или выходу логической функции. Данное назначение весьма полезно при моделировании системы. Для назначения зонда используют команду Assign /Probe.

Connected pin assignment (назначение соединённых выводов) задаёт внешнее соединение двух или более выводов. Эта информация также полезна в режиме тестирования временных параметров и при тестировании нескольких скомпонованных проектов. Для выполнения назначения соединённых выводов используют команду Assign/Connected/Pins.

Local routing assignment (назначение местной трассировки) присваивает коэффициент разветвлению по выходу узла логического элемента, находящегося в том же блоке или же в соседнем, смежным с выбранным узлом, с использованием общих местных связей. Местная трассировка так же производится между узлом, помещённым в блок на периферии устройства, и выходным контактом, с которым он соединён. Назначение местной трассировки производится с помощью команды Assign/local routing.

Device assignment (назначение устройства) назначает тип ПЛИС, в которой будет воплощён проект. Если проект состоит из нескольких устройств, данная функция осуществляет назначения чипов конкретным устройствам. Можно также выбрать опцию AUTO и предоставить компилятору выбрать устройство из заданного семейства устройств. Процессом автоматического выбора устройства можно управлять, задавая диапазон и число устройств в семействе. Если проект оказался слишком большим для реализации в одном устройстве, можно задать тип и число дополнительных устройств. Для выбора устройства используется команда Assign/Device.

Logicoption assignment (назначение логической опции) управляет синтезом отдельных логических функций во время компиляции с применением стиля логического синтеза и/или отдельных опций логического синтеза. Фирма Altera обеспечивает большое количество логических опций, а так же готовых стилей, каждый из которых представляет собой собрание установок для логических опций, объединённое одним именем стиля синтеза (Synthesis style). Пользователь может применять готовые стили или создавать новые, которые позволяют настраивать опции синтеза на определённое семейство устройств, учитывая при этом архитектуру семейства. Для настройки стилей синтеза применяется команда Assign/Logic Options.

Timing assignment (назначение временных параметров) управляет логическим синтезом и подгонкой отдельных логических функций для получения требуемых значений времени задержки Пользователь может также вырезать соединения между путями распространения для конкретного сигнала и другими ячейками (блоками) проекта. Назначение временных параметров блока производится по команде Assign/Timing Requirements.

Кроме использования команд меню Assign, назначения можно выполнять щелчком правой кнопки мыши по выбранному узлу проекта и выбирая соответствующее назначение во всплывающем меню.

Можно определить глобальные опции устройства для компилятора, для того чтобы он их использовал для всех устройств при обработке проекта. Для резервирования дополнительных возможностей логики на будущее можно задать процентное соотношение выводов и логических элементов, которые должны оставаться неиспользованными во время текущей компиляции. Можно также задать установки для битов опций устройств и выводов в конфигурации устройств, используемой для нескольких целей. Например, можно задать бит защиты от несанкционированного считывания (Security Bit) по умолчанию глобальным, что предотвратит пиратское копирование топологии устройств, базирующихся на памяти EPROM или EEPROM.

Помимо задания локальных назначений, возможно, задать назначения для всего проекта, используя так называемые глобальные назначения (Global Assignments). Можно ввести глобальные временные требования для проекта, задавая общие характеристики для времени задержки. Можно также удалять соединения между любыми двунаправленными контурами обратной связи, цепями прохождения сигналов Present (установка 1) и Clear (установка 0) и другими цепями синхронизации в проекте. Для этих целей используется команда Assign/Global Project Timing Requirements.

Можно сделать глобальные установки для компилятора в части логического синтеза проекта. Можно задать используемый по умолчанию стиль логического синтеза, определить критерий оптимизации либо быстродействие (Speed), либо занимаемым местом на кристалле (Area), дать указания компилятору по выбору автоматических глобальных сигналов управления, таких, как Clock (тактовый), Clear (установка 0), Preset (установка 1) и Output Enable (разрешение выхода). Для назначения глобальных параметров логического синтеза используют команду Assign/Global Project Logic Synthesis.

Вопросы для проверки усвоения материала

1. Какие два каталога имеет система MAX+PLUS II?

2. Из каких подкаталогов состоит каталог maxplus2?

3. Из каких подкаталогов состоит каталог max2work?

4. Какое полное название имеет система MAX+PLUS II?

5. Перечислите состав программного обеспечения системы MAX+PLUS II.

6. Процедура разработки нового проекта в системе MAX+PLUS II.

Вместе с этой лекцией читают «Лекция 2».

7. Приложения системы MAX+PLUS II.

8. Способы описания файлов проекта в системе MAX+PLUS II.

9. Общие функции для всех приложений MAX+PLUS II.

10. Типы назначений при управлении компиляцией проекта и его временных параметров в системе MAX+PLUS II.

Литература

1. Стешенко Б.В. ПЛИС фирмы АLTERA: проектирование устройств обработки сигналов. –М.: ДОДЭКА, 2000. –128 с. (38-50 с.)

�. �������

�������� ������� ������� ����� ����������� �������� ��������� �������, ��������� � ���������� ������� ���������� � ������������� ����������. �������� �� ������ �������� ��߸� ���������� � «Chip News» �� ������� ������������������� �������������� (����) MAX+PLUS II [1-5], ������� ������������� � ���� ���� �� ����������. ����������� ������ �������� ������������ ������� �������.��������� �� ������������� ����� ���� ����� ALTERA � ���� MAX+PLUS II ��� ���������� �������� ��������� �� ���� ������� ���� ����� ��������� ��������� ����������� ��������� � ����� ���������-����������. ������� ����������, �� ��������� ����������� ����������� ��������������, ������ ���� � ����� ���������� �������. ����� ����� �� ������ ������������� ������������� � �������� ����� ���������� ������������ �����������. �������� �������� �� ���������� ���� � ����� �������� �������� ��������� AHDL ����� ����� � [6,7].

���� MAX+PLUS II ������������� ��� ���������� �������� ��������� � ������������� ��� ������� ���� ������ ��������� �����������:

- �������� �������� �������;

- �������� ���������� �������;

- �������� ����������� �������;

- �������� ���������������� («����������») ����.

���������� �������� �������������� � ���� MAX+PLUS II �� ������� ���������� ����ݸ����� ��-����������������. ����� ������ ������� �������� ������� 4 ���. ���������� �������� �������� ������� ������� (���), �������� ������� ������� (���), �������� ������������ (���) � �������� ������������� (���). ��� ��� ������ ��������� ��������������: ������ � = 20 ��, ������������ �������� �� = 1,6 ��; ��� � = 20 �� — �� = 68 ���. ��� ������ ������������� �� ������ ���. ��� ��� � = 64 ���, �� = 12 ���. ��� ����� ��������� ���������: � = 64 ���, �� = 4 ���. ��� ������ ���� �������� � ������ ���. � ���� ������� ������� ������� ��������� �������������� �� ������������� ���� 7845-79, �� ��-�� ��������� ������ � ���� ���ĸ��� ���������.

���������� ������ ���������� ���������� � �������������� �����. �� ������������ ������� �������, ��� ��� ��������� ��� � ��� ����������� ����� � ������������� ������� � = 20 ��/250 �� = = 80000. ��� ������������ ��� � ��� ���������� ������ � � = 64 ��� / 250 �� = 256. ������ ������ ���� �����������, ��������� �������� ������� ���� ����������� ��������� � �������� ������� ���������� ָ�����. ����� ���� ���������� ��������� �������������� �����, ������� ����� ��������������� ��������� ������� � �������� ��-�������������.

� [1] ��� ����������, ��� �������������� ������ � ����������� ��������� �������� ������������������. ���� � ����� ������� �������, ��� ��� ����������������� �������� � ������ ������ ����� ����� [2], �� ���θ� ���������� � �������� ���������� ����� ��������� ks1.tdf (���. 1) �� ����� AHDL. ������� ��� � ���, ��� ������������� ���������� ������� ���������� ���������, � �������� ���������� �������������� ����� ������ �����. � ���� �� �������� ������������ �������. ������, ��������� ������ ������ � ��������� ��������� ���� �� ������� �� ��� �� ����� �������: �������� �����������. ������� ���������� ������ ��������� ���������� ������ ����, ���� ��� ����� ����������, ������-�����������.

��������� ks1.tdf ��������� ������ ���� ���������� ������� Q, Y � ����������� ���������� ������� ��������� ��-���������������.

������� 1. �������� ����� ks1.tdf

SUBDESIGN ks1

(

q7,q8,q9,q10,q11,q12,q13,q14,q15,q16 : INPUT;

y4,y5,y6,y7,q4,q5,q6 : INPUT;

sgi,kgi,ssi,ksi,reset,strob96 : OUTPUT;

)

BEGIN

reset = q7&q11&q12&q13&q16;%k=80000=h13880,T=20��%

TABLE

q8,q9,q10,q11,q12,q13,q14,q15,q16 => kgi;

x, x, x , 0 , x , 0 , 0 , 0 , 0 => 1 ;

x, x, x , x , 0 , 0 , 0 , 0 , 0 => 1 ;

0, 0, 0 , 1 , 1 , 0 , 0 , 0 , 0 => 1 ;

END TABLE;

TABLE

y4,y5,y6,y7 => sgi;

1 ,x ,1 ,1 => 1;

x ,1 ,1 ,1 => 1;

END TABLE;

ssi = sgi & !y4;

ksi = kgi & q11&(!q10&q9&q8#q10&!q9&!q8&!q7&!q6&!q5&!q4);

strob96 = (!q7#!q8)&!q9&!q10&!q11&!q12&!q13&!q14&!q15&!q16;

% 96���=>384=h180 %

END;

����� ����, ��� ��������� ks1.tdf �������� � ��������, ���������� ������� Ÿ Include-���� � ��������������� ��� ������ ������������� ��������, ����� ����� �������� � ����������� ���������. ������ � θ� �������������� ����� ��������� ������������� �������.

�������� Include-����� � ������� ������������� ��������:

- ������� ���� .tdf � ��������������� ���;

- ݸ������ «�����» �� ������� File/Create Default Include File;

- ��������� ���� ���� � �������� �������� ������/�������;

- ݸ������ «�����» �� ������� File/Create Default Symbol.

����� ��� � ����������� ��������� ������������ ��� ����� ������� � �������������� ������ ��� ����������� ������������� �������� (���. 2). ����� ���������� � ������� ���������� ���� �������� ��������� ��������� (���. 3), ��������� ��������������� �� �� ��-���������������. �� ��������� ������� ������� ����������� ���������� �������� � ���������������� ���� (��. ���� ���������� �� ������ MAX+PLUS II).

������� 2. ����� ����������������

��� �������� ������ �������������� ����� � ����������� ���� ���������� ��������� ��������� �������. �������� ������ �������� ������� ������ ���� �� ����� 40 ��. ��� ��������, ��� ��� ����� ������� �����������. � �������� ������ ������ ����� ������������ �� ��������� 1533��1. ����������� ����������� ������� �� ���� ������ ������ (24 ��), �� ��������� �������� ���������� 12 ��. ���������� ������������ ������ ����. ��� ���� ���� ����� ������������ 1533��8 ��� ����� ������ �� � �� ����� ������������� �����������. � �������� ��������� ���������� ���������� ��������� �� ���������� ���������� ��56�.

������� 3. ��������� ��������� ����������������

� ���������� �����ĸ� ������� �������������-���������� �������� �� ���� MAX+PLUS II ��� �������������, �� ������� �������� ��������� ������������.

���������� �� ������ MAX+PLUS II

����������� ����������� ������� MAX+PLUS II �������� 11 ���������� � ������� ����������� ���������. ��������� ����������, �������������� �������� �������, ����� ���� �������������� ���������, ��� ��������� ������������ ������������� ����� ���� ������� «����» ��� � ������� ������ ����. � ��� �� ����� ����� �������� ���� �� ������� ����������, ��������, ����������, ���������, ���������� ������������� � ������������. ���� � �� �� ������� ������ ���������� �������� ���������, ��� ��������� ������ ���������� ����������� �������.

Hierarchy Display — ����� �������� — ���������� ������� ������������� ��������� ������ � ���� ������ � �������, ��������������� ����� ����������.

Graphic Editor — ����������� �������� — ��������� ������������� ������� ���������� ������ � ������� ��������� ����������� �� ������ WYSIWYG.

Symbol Editor — ���������� �������� — ��������� ������������� ������������ ������� � ��������� �����.

Text Editor — ��������� �������� — ��������� ��������� � ������������� ��������� ����� ����������� �������, ���������� �� ������ AHDL, VHDL, Verilog HDL.

Waveform Editor — ���������� �������� — ��������� ������� �������: ���������� ��� ���������� ������� � ���������� ��� ����� �������� �������� � ���������� ����������� ������������.

Floorplan Editor — ����������� ����������� — ��������� ������������ ���������� ������ ���������� ��������� ���������� � �������� ���������� ���������.

Compiler — ���������� — ������������ ����������� �������.

������ � ����������� ����������

������ ����������� ��������, ��������� ����� ���� (��� � Word). ������� ������� � ���� ��������� ������� ����������. �� ������ ����� ����� �������� � ����������� mf, ������� �������� ����������� �������� ����� 74��. ����� ������ ������������� �������� ����� ����������, �������� ������� ������ �� ���������� ��������. ����� ����, ����� ���������� ����������, �������� ��������� ��������:

- �������� ������ ������� ������� «����»;

- ݸ������ �� ���� ������ �������� «����»;

- ������� � ����������� ���� ����� Edit Ports/Parameters�;

- ������� Help on.

� ���� ����������� ������� �������� ������� ��� ���������� ��������� � ������� ���������� ��� ���������� ��������.

��� ������ � ������������ ���������� ��������� ��������� ��������:

- ������� ������ ������ �� ���������� �����������;

- ������ �������� «����» ݸ������ ������ �������;

- ��������� ����������� ���������, �������� ������ �����.

����������� �������� Altera ����� �� �������� PaintBrush. �� ������ �������� ����� ���� �����������.

���������� ��� ����������� ����� ������� Options/LineStyle � ������� ���� �������������� �����. ����������� ���� ����������� ��������� � ������ ��������� (��������� ������� � ����� ���������������� ����), �� ����� ��� ������ � ��������� ������, �������� ������ � ������ �����/������ ��� ��� ����������� ������. ��������, rg[12..1], ��� 12 � 1 — �������������� ������� � ������� ������� ������. ����������� ��������� ����� � ���� ������� �� ����� ���� � Ÿ �������, �������� rg[1]. �����, ������ �� ������/������� ����� �� ����������, ��� ��� �� ������������� ������������� ����� ������/�������.

����� � ������ �������� � ������� ����������, ������� ���������� ������� �������. ��� ����� ������ ���� �����������.

����� �� ���� ��� ����� �������� � ������� ���������������� ������� �����.

����� ����� ��������� � ������� ����������� � ���� ������� ����.

� ������� ���������� ����� ������� GND � VCC («�����» � �������). ��������� ���������� ������� ������� ����� ������� «����».

�������� �������� ����������� �������� Rotate, ���������� �� ����, ������� ���������� ����� ������ ������ �������� «����» (����������� ����). ����� ��������� ������� �������� �� ����� Edit.

���������� ���� �� ������������ ���������:

- ��������� �� ������� ������� �����������, ����� ���������� ����������� ������ ����� � ������ ������������ �������;

- � ����� File������� Size� ���������� ����������� ������ �����. ��� ����� ������� ������� �������� ������������ ��������;

- ���������, ���������� �� � ���� ����� ��� �����;

- ����� � ����� File� ������� Print Setup��� ��������� �������� ��� ���������� ������������;

- ݸ������ �� ������ ��������.

�������� ������������� ��������:

- ������� ���� .gdf � ��������������� ���;

- ݸ������ «�����» �� ������� File/Create Default Symbol.

���������� �������������� ������� � ����������� ���������:

- ���������� ��� ����� (������������) � ���� ������ *.gdf;

- �������� ���������� ������� ����� (������������);

- � ������� ������� File/Create Default Symbol������� ������ ���� (������������) � ���� ���������� ����������� � ���� �������;

- �������� ���� ������ ��� ������� ����������� ������� � �������� (main) ���� (���������);

- �������� ��� ����� � ���� ��������� � �������� �����.

������ � ��������� ����������

���� �������� ������� ����� � ����������� *.tdf. ����� ������������ ����� AHDL � VHDL.

��� ��������� include-������ ����� ݸ������ �� ������ � ������������ �����, ������� ���������� maxplus2max2inc ��� ����� All files � ����������� ����� � ����������� *.inc. �� ���������� ����� ������� � ���������� maxplus2 max2libmf. ����� ������� ���������� function (include), ����� ݸ������ �� ����� Templates (���. 121, �. 1 ����. ��������).

�������� Include-�����:

- ������� ���� .tdf � ������ TITLE � ��������������� ���;

- ݸ������ «�����» �� ������� File/Create Default Include File;

- ��������� ���� ���� � �������� �������� ������/�������.

�������� Include-����� �� ����������� ����������:

- ݸ������ �� Help;

- ������� ����� Searh for Help on�;

- ����� ��� ��������� (4count, 8count � ��� �����);

- ݸ������ �� ������ «��������»;

- ����������� ����������.

�������� Include-����� �� ����������� ����������:

- ������� ����� � ������� Include-������;

- ������� ���� Include-����;

- ����������� ����������.

��������� �� ���� ����� MAX7000S:

- ����� � ����� Assign / Device;

- ���������� � ���� Device Family��� ���� MAX7000S;

- ������ ����� ���� ��� ������� � ��������� ����������.

�������� ���������������� �������

������������ �������������� ������� � �������������� ������������ � ���������� ���������� ������������. ����������� ���� (������, ��������, ��������� � �. �.) ������ ��������� � ����������� ���������. ���������������� �������� (���), ������������ ���������� �������, �������� � ���������, ������� � ��� ����� ����� ������������� � ��������� ���������. ��� ����� �������������� ���������� �����, � ����� ���������� ���������� ����������. ������� ������� ������ � ���� ������ ����� ���� ���������:

- ������� ����� �� ����������� ���� � ������������� �����;

- ������� � ��������� ��������� ������(�), ����������� ��� ������������� �����;

- ��������������� ��������� ����(�) � ��������� ������ ������� � ������� ������, ��������������� ������� �������������� �����;

- � ����������� ��������� ������� ���� � ���������� ������, � ������� �������� ��� ������������� ����� � ���� �������� � ��� ����������� ����;

- ��������������� ���������� ����.

���������� � �������

����� ����������� � ����� File/ Project ������ ��� ������� (��� ��������� ����� � ����������� *.gdf). ���������� ���������� ���� ����� ����� MAX+plusII/Compiler, ���� ����� ������� ���������������� �������. ��� ��������� ���� ����������� ����� ݸ������ �� ������� Start.

��� ������� ������ � ������������� ����� ���������� ��������������� ���������. ������� ������ ��������� � ݸ����� �� ������ Location, ����� ������������ ������.

��� ������ ���������� ������ ������������, ������ � ������ ��������� ����� � ���� ������� ����� Assign, � � ��� Global Project Logic Synthesis � ������ ��� «�������» � ������� Automatic Global, MAX Device Synthesis Options � ������. ���������, ��� � ���� Global Project Synthesis Style ���������� ����� NORMAL. � ���� ������ ���������� ����� ����� ������������ � �������� �������.

��� ����������� ��߸�� ������� ���������� ��������� ��������� ��������:

- ݸ������ «�����» �� «��������»;

- ������� ����� rpt;

- ����������� ��������� �� ����� %LCS Utilized.

�������������

��������� ���� � ����������� *.s�f, ݸ����� �� ���������������� ������ ������� ���������������� �������. ������� ������� �������� ���� ����� �������/�������� ����������.

��� ��������� ��������� ������� ������������� ����� ����� � ����� File/EndTime � ��������� ������ ����� (us, ms, s) ��� ������� (1, 10, 100, 1000).

��� ������� �������� ������� ����� ������������ ����� ���������������� ������� (������ � �������� «�»), �������������� ������� ������� ��������� �������� �������.

��� ��������� �������� ������� �������� ����� � ������� ������������� ������ ���������� ������� � �������������� ������������ �������, � ����� � ��� �������� � ������� ������ � �������� «1» �� ����� ���������������� ������.

���� ��� ��������� ������� �� ����������� ������� ����, �� ݸ������ �� 3-�� ������ ������ �� �������������� ���������������� �������, � ����� ����� �� ������������ ������� ��������� ������� �������.

��� ������� ������ ������������� (���������) ���������� ݸ������ �� ������ ���������� ������� ���������������� ������.

���������� ��������

��� �������� ��������� ������� ������� ��������� ��������� ��������:

- ����� � ���� Assign;

- ������� �����Pin/Location/Chip�;

- � ����������� ���� �������� ��� ���� � ����� ������ ����.

����������� ���������� ����� ������ �� ������������� �������� �����, ������ ���� .acf, ��� — ��� �������.

���������������� ����

����� ���������� �������� �������� ���������������� ����. ���������������� ����������� � ��������� �������:

- ��� ����������� �� ������������ ������ ByteBlaster � ����������� ���߸�� �� � ���������������� �������;

- �������� ��, ��������� MAX+PLUS II;

- ������ ������� (������ +5 �) �� ��������������� ������;

- ����� � ����� ���� File� ������ ��� �������;

- ������� ����� MAX+plus II/Programmer� ������ Program ��� ������ ݸ������ «�����» �� ������ ����������������;

- ��������� � �������� ���������� ����������������;

- ��������� ������� ���������������� �������;

- ����� �� MAX+PLUS II;

- ��������� ��;

- ����������� ������ ByteBlaster.

����������

- �������� �. ����� ���������� ���������� �������� ��������� �������� �� ���� // Chip News. 1999. � 8 � � 10. 2000. � 1 � � 3.

- ����� �. ����������� ��������� �������� ������ ������������������� �������������� � ������� ����������� // Chip News. 1997. � 1. �. 12�15.

- ������� �.�. � ��. ����������� ���������� ���������� �������� ���������� �� ������ ���� ����� ALTERA // Chip News. 1997. � 9-10. �. 26�33

- ����� � ��. ���������������� ������� �� ���� ������������������ ��� // Chip News. 2000. � 7. �. 51�53.

- ������� �.�. ����������� ������� ������������ ���� MAX+PLUS II // Chip News. 2001. � 1. �. 56�58.

- �������� �.�. ���� ����� ALTERA: �������������� ��������� ��������� ��������. �., 2000.

- ������� �.�. ���� �������� �������� ��������� AlteraHDL. �., 2001.

- ������� �.�. ���������� ������ ���������� �������� ���������. �., 1977 (���� �����. ��������. ���������� — W1454/231) (���� ����. ������ — 507/�68).

Начинаем мучения с MAX+plus II[править]

1. Создаем папку для проекта (файлов будет ОЧЕНЬ много, рекомендую)

ВНИМАНИЕ!!! Путь к папке проекта(впрочем как и название самой папки) не должен содержать русских букв, иначе зря паримся. Ферштейн?

2. Запускаем MAX+plus II и создаем новый проект File->Project->Name [Ctrl+J]. В окне указываем созданную папку и вводим имя, например xcnt.

3. Создаем файл с описанием проектируемой логической схемы, File->New; {File type = Text Editor File}. Откроется окно текстового редактора.

4. Свяжем созданный пустой (пока) файл с проектом, File->Project->Set Project to Current File [Ctrl+Shift+J]

Заметим, что в заголовке текстового редактора появилось вместо Untitled.tdf xcnt.tdf

5. Набираем описание. ВНИМАНИЕ! Имя проектируемого элемента в директиве SUBSET должно совпадать с названием проекта, то есть xcnt

% Счетчик с коэффициентом пересчета 264, используются только примитивы AHDL Параметры выходного импульса не заданы, поэтому выбраны исходя из простоты решения % TITLE "Counter 264"; CONSTANT COEF = 264; -- Коэффициент пересчета % Внимание! При изменении коэффициента пересчета в меньшую сторону возможно придется изменить условие лог.1 на выходе (строка Out = ...) % SUBDESIGN xcnt ( Out : OUTPUT; -- Выход счетчика Clk, Reset: INPUT =GND;-- Счетный вход и вход сброса ) VARIABLE TR[9..1] : TFF; -- Массив T-триггеров Res_int : NODE; -- Внутренняя связь - асинхронный сброс счетчиков BEGIN TR[].(CLK, PRn)= (Clk, VCC); TR[].CLRn = !(Reset OR Res_int); -- Двоичный счетчик с параллельным переносом TR[1].T = VCC; TR[2].T = TR[1].Q; TR[3].T = TR[1].Q&TR[2].Q; TR[4].T = TR[1].Q&TR[2].Q&TR[3].Q; TR[5].T = TR[1].Q&TR[2].Q&TR[3].Q&TR[4].Q; TR[6].T = TR[1].Q&TR[2].Q&TR[3].Q&TR[4].Q&TR[5].Q; TR[7].T = TR[1].Q&TR[2].Q&TR[3].Q&TR[4].Q&TR[5].Q&TR[6].Q; TR[8].T = TR[1].Q&TR[2].Q&TR[3].Q&TR[4].Q&TR[5].Q&TR[6].Q&TR[7].Q; TR[9].T = TR[1].Q&TR[2].Q&TR[3].Q&TR[4].Q&TR[5].Q&TR[6].Q&TR[7].Q&TR[8].Q; IF (TR[].Q == COEF - 1) THEN -- Если досчитали до [коэффициента пересчета - 1], то есть на вход пришло ((COEF-1) + 1) импульсов Res_int = VCC; -- начинаем счет с 0 ELSE Res_int = GND; -- Иначе - сигнал сброса не активен END IF; Out = TR[9] AND TR[3]; END;

6. Сохраним и проверим описание, File->Project->Save & Check [Ctrl+K]. Появится окно, в котором указано количество ошибок и замечаний, выявленных при проверке. Описания ошибок и замечаний находятся в окне с заголовком Messages — Compiler.

7. Если все OK, компилируем проект File->Project->Save & Compile [Ctrl+L], иначе — к п.5

8. Можно приступить к симуляции. Откроем редактор временных диаграмм (Waveform Editor) MAX+plus II->Waveform Editor

ВНИМАНИЕ!!! Если такого пункта там не имеется в наличии и когда завезут не сказано, то надо скопировать файлик cpt.dll из папки, откуда устанавливали, в папку с устанновленным Max+plusII. И все.

9. Чтобы добавить сигнал, можно дважды кликнуть ЛКМ по пустому месту под разделительной линией, а можно с помощью контекстного меню (клик ПКМ) Insert Node…

Чтобы отобразить список доступных сигналов есть кнопка List, но настоящие гуру не боятся трудностей и набирают названия и тип сигнала вручную. Если же выбрать название сигнала из появившегося списка, то все параметры подставляются автоматически. Для начала выберем Reset (в скобках — I, то есть это вход) OK. Аналогично нужно добавить все сигналы из списка.

Hint Если список не появился, значит проект не скомпилирован

10. Установим форму входных сигналов, в нашем случае это сигнал сброса Reset и взод тактовых импульсов Clk. Можно отключить привязку к сетке, чтобы делать сигналы произвольной длительности Options->Snap to Grid. Выбрать основной режим (слева вверху должна быть активна стрелочка), теперь удерживая ЛКМ можно выделить отрезок временной диаграммы. Затем можно установить значение на этом участке либо в 1, либо в 0 (кнопки слева с 0 и 1). Нужно сделать единичный импульс сброса.