[4] CPU, CLOCKS + EEPROM + STRAPPING

[21] MEMORY, A MIRRORED (BOTTOM)

[23] MEMORY, B MIRRORED (BOTTOM)

[25] MEMORY, C MIRRORED (BOTTOM)

[27] MEMORY, D MIRRORED (BOTTOM)[28] ANA, CLOCKS + STRAPPING[29] ANA, VIDEO + FAN + JTAG

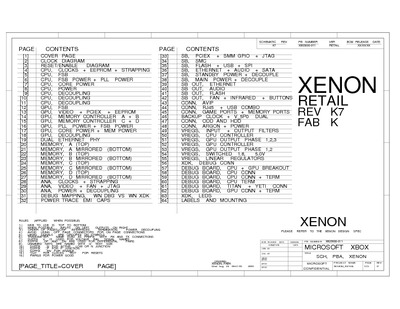

K7 X803600-011 RETAIL XX/XX/XX

XENONRETAILREV K7

SCHEMATIC REV PB NUMBER VER BOM RELEASE DATE

FAB K[49] VREGS, INPUT + OUTPUT FILTERS

[51] VREGS, GPU OUTPUT PHASE 1,2,3[52] VREGS, GPU CONTROLLER[53] VREGS, GPU OUTPUT PHASE 1,2

[57] DEBUG BOARD, CPU + GPU BREAKOUT

[60] DEBUG BOARD, CPU TERM[61] DEBUG BOARD, TITAN + YETI CONN

[63] XDK, LEDS[64] LABELS AND MOUNTING

4.) AVOID USING OFF PAGE CONNECTORS FOR ON PAGE CONNECTIONS

[PAGE_TITLE=COVER PAGE]

14.) ‘CLK’ FOR CLOCKS, ‘RST’ FOR RESETS13.) SUFFIX _EN FOR ENABLE

9.) UNNAMED NETS ARE NAMED WITH /2 TEXT SIZE

7.) SUFFIX V_ IS USED FOR VOLTAGE RAIL SIGNAL NAMES

5.) LANED SIGNALS ARE GROUPED ON SYMBOLS

2.) WHEN POSSIBLE: INPUTS ON LEFT, OUTPUTS ON RIGHT

RULES: (APPLIED WHEN POSSIBLE)

[32] POWER TRACE EMI CAPS

[19] DUAL ETHERNET PHY[18] GPU, DECOUPLING[17] GPU, CORE POWER + MEM POWER

[14] GPU, MEMORY CONTROLLER A + B[13] GPU, VIDEO + PCIEX + EEPROM[12] GPU, FSB[11] CPU, DECOUPLING[10] CPU, DECOUPLING

[9] CPU, DECOUPLING[8] CPU, POWER[7] CPU, CORE POWER[6] CPU, FSB POWER + PLL POWER[5] CPU, FSB

[3] RESET/ENABLE DIAGRAM[2] CLOCK DIAGRAM[1] COVER PAGE

PAGE

[35] SB, FLASH + USB + SPI[36] SB, ETHERNET + AUDIO + SATA[37] SB, STANDBY POWER + DECOUPLE

XENON

[38] SB, MAIN POWER + DECOUPLE[39] SB OUT, ETHERNET[40] SB OUT, AUDIO[41] SB OUT, FLASH

[33] SB, PCIEX + SMM GPIO + JTAG[34] SB, SMC

[42] SB OUT, FAN + INFRARED + BUTTONS[43] CONN, AVIP[44] CONN, RJ45 + USB COMBO

[15] GPU, MEMORY CONTROLLER C + D

3.) ORDER OF PAGES=CHIP INTERFACES, TERMINATION, POWER, DECOUPLING PLEASE REFER TO THE XENON DESIGN SPEC

[24] MEMORY, C (TOP)

[22] MEMORY, B (TOP)

[48] CONN, ARGON + POWER[47] CONN, ODD AND HDD[46] BACKUP CLOCK + V_5P0 DUAL[45] CONN, GAME PORTS + MEMORY PORTS

6.) TRANSIMITTER NAME USED AS PREFIX WITH RX AND TX CONNECTIONS

1.) MSB TO LSB IS TOP TO BOTTOM

15.) PWRGD FOR POWER GOOD

[30] ANA, POWER + DECOUPLING

[56] XDK, DEBUG CONN

CONTENTS

[16] GPU, PLL POWER + FSB POWER

[20] MEMORY, A (TOP)

[26] MEMORY, D (TOP)

12.) SUFFIX _P FOR P JUNCTION

8.) SUFFIX _DP AND _DN ARE USED FOR DIFFERIENTAL PAIRS

[31] DEBUG MAPPING, WN DBG VS WN XDK

10.) SUFFIX _N FOR ACTIVE LOW OR N JUNCTION

[55] VREGS, LINEAR REGULATORS

[58] DEBUG BOARD, CPU CONN

[62] DEBUG BOARD, GPU CONN + TERM

[59] DEBUG BOARD, CPU CONN + TERM

[54] VREGS, SWITCHED 1.8, 5.0V

[50] VREGS, CPU CONTROLLER

CONTENTSPAGE

XX/XX/XX

SCH, PBA, XENON

X803600-011

XENON_FABKXENON_RETAIL 1/73 K7Wed Aug 24 09:41:55 2005

PAGEMICROSOFT REV

CONFIDENTIAL

PROJECT NAMEDRAWING

BOM RELEASE DATE

TITLE

DATE

ENGR

SIGNATURE

APVD

CHK BY

PB NUMBER

DRN BY

APVD

APVD

MICROSOFT XBOX

ENETPHY

SB

VMEM VR

5P0 VR

3P3 VR

1P8 VR

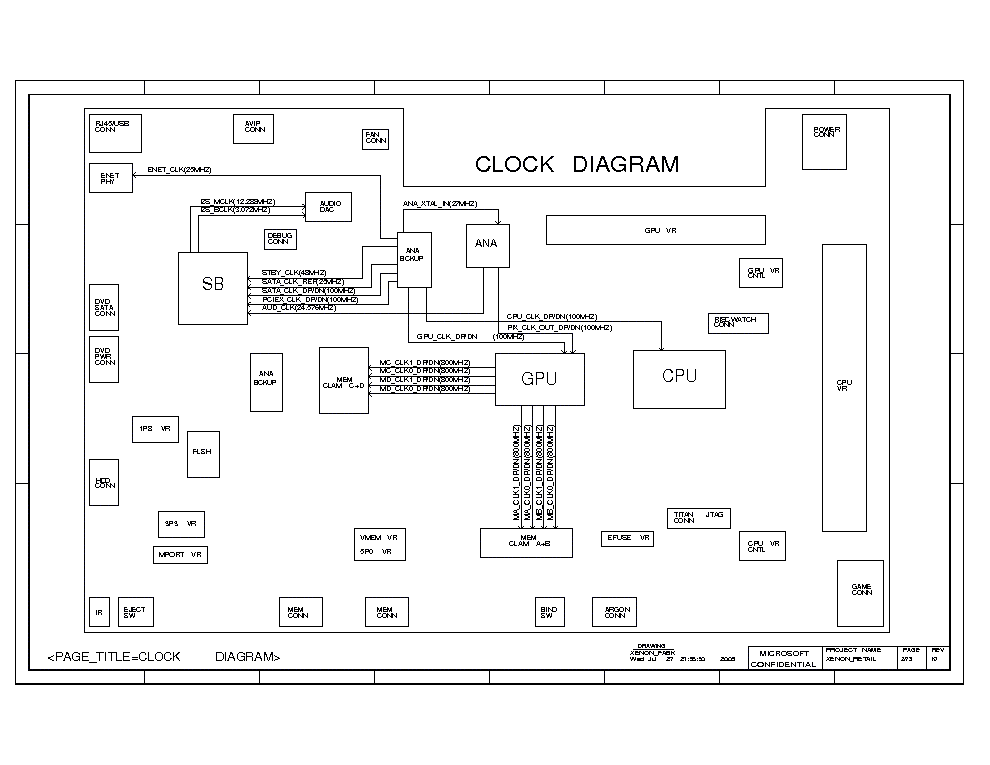

<PAGE_TITLE=CLOCK DIAGRAM>

MPORT VR

I2S_MCLK(12.288MHZ)

ENET_CLK(25MHZ)

ANA_XTAL_IN(27MHZ)I2S_BCLK(3.072MHZ)

HDD

SATA_CLK_DP/DN(100MHZ)SATA_CLK_REF(25MHZ)STBY_CLK(48MHZ)

AVIPCONN POWER

PCIEX_CLK_DP/DN(100MHZ)AUD_CLK(24.576MHZ)

MEMCLAM C+D

AUDIODAC

BCKUPANA

DEBUGCONN

GPU_CLK_DP/DN (100MHZ)

MC_CLK1_DP/DN(800MHZ)

GPUANABCKUP

FLSH

EJECTSW

CPU

MB

_CLK

0_D

P/D

N(8

00M

HZ)

MB

_CLK

1_D

P/D

N(8

00M

HZ)

MA

_CLK

0_D

P/D

N(8

00M

HZ)

MA

_CLK

1_D

P/D

N(8

00M

HZ)

CONN

CONN

IR

PWRCONN

DVDSATA

DVD

RJ45/USB

MEM MEMCONN SW

BIND

CLAM A+BMEM

CONNARGON

EFUSE VR

CONN

GPU VR

CONNTITAN JTAG

CPU VRCNTL

CONNGAME

CONN

GPU VRCNTL

RISCWATCH

CPUVR

CONNCONN

FAN

CLOCK DIAGRAM

CONN

MD_CLK0_DP/DN(800MHZ)MD_CLK1_DP/DN(800MHZ)MC_CLK0_DP/DN(800MHZ)

CPU_CLK_DP/DN(100MHZ)

ANA

PIX_CLK_OUT_DP/DN(100MHZ)

K72/73XENON_RETAILWed Jul 27 21:53:30 2005XENON_FABK PAGEMICROSOFT REV

CONFIDENTIAL

PROJECT NAMEDRAWING

RJ45/USB

SB

_RS

T_N

3P3VR

5P0 VR

VMEM VRVREG_1P8_EN_N

VR

EG

_3P

3_E

N

SM

C_D

BG

_EN

VR

EG

_CP

U_P

WR

GD

DEBUGCONN

CONN

DVD

HDDCONN

SATADVD

EX

T_P

WR

_ON

_NAUD_RST_N

VREG_GPU_EN_N

DACAUDIO

EXT_PWR_ON_N

GPU_RST_DONE

MEM_RSTMEM_SCAN_EN

GPU

ME

M_R

ST

ME

M_S

CA

N_B

OT_

EN

ME

M_S

CA

N_T

OP

_EN

ME

M_S

CA

N_E

N

MEM_SCAN_TOP_EN

SB

MEM_SCAN_BOT_EN

RESET/ENABLE DIAGRAM

GPU_RST_N

CLAM A+B

CLAM C+DMEM

SMC_RST_N

TITAN JTAGCONN

ARGONCONN

VREG_EFUSE_EN

ANA_CLK_OEANA_RST_N

AVIP

CPU_CHECKSTOP_N

ANA

AUD_CLAMP

PWR

PSU_V12P0_EN

CPU

CPU_PWRGD

EFUSE VR

MEM

RISCWATCH

CPU_RST_NCPU_PWRGD

VREG_CPU_EN

CNTLCPU VR

GPU VR

CONNFAN

MEM

CONN

BIND

CONN

GAME

IR SWEJECT

SWCONNMEMCONN

CPU

CONNPOWER

ENET

VR

GPU VR

CONN

CNTL

CONN

CONN

ENET_RST_NPHY

VREG_5P0_EN_N

VREG_GPU_PWRGD

[PAGE_TITLE=RESET/ENABLE DIAGRAM] K73/73XENON_RETAILWed Jul 27 21:53:44 2005XENON_FABK PAGEMICROSOFT REV

CONFIDENTIAL

PROJECT NAMEDRAWING

CPU, CLOCKS + EEPROM + STRAPPING

N: STUFF C?,C? WITH .01UF CAPS FOR SHIVAN: STUFF C?,C? WITH ZERO OHM R’S FOR WN

LAYOUT: MUST BE ACCESSIBLE

[PAGE_TITLE=CPU, CLOCKS + EEPROM + STRAPPING] K74/73XENON_RETAIL

4

4949

4

56

4

49

4

34

49

34

55

4

4

29

4

4

4

46

46

4

29

4

4949

Wed Aug 24 09:27:00 2005

2 1R7F7

2

1C7R113

2

1 C7R112

1FT7T7

1FT7R5

1FT7R1

1FT7R2

1FT7R6

1FT7R4

21

TP6D1

2

1

R7U3

2

1 C6R46 2 1R6R10

1FT7T5

1FT7T3

1FT7T41

FT7T1

1FT7T2

1FT2P12

1FT2P11

2

1R7F4

2

1R7F3

2

1R7R2

2

1R7R1

2

1R6R9

21 R7R11

21 R7R10

21 R7R16

21 R7R4

2

1

R6E1

2

1

R6D1

1

DB7R1

21

TP7R221

TP7R421

TP7R3

21

TP7R1

654321

J7F1

2

1R7D1

R7F2

R6E2

R7E7

2 1R7F1

2 1R7E8

2

1 C6F1

2 1R6R5

2 1R6R4

2

1

R7R17

2

1

R7R18

2

1

R7R19

2

1

R7R3

2

1

R7R5

2

1

R7R20

2

1

R7R23

2

1

R7R22

2

1

R7R13

2

1

R7R12

2

1

R7R21

3

8

256

7

41

U7E1

21

TP6R2

21

TP6R1

2

1

R7R6

2

1

R7R15

2

1

R7R7

2

1

R7R8

21 R7R24

2

1

R7R14

2

1

R6D2

2

1

R7R9

2

1

R6R8

2

1

R6R6

2

1

R6R7

C5A5B4A4B5C4

AJ4AK5

AH13AK12

AG16

AK20AK21

AH4

AH1AK3

A3

B3B2A2

AJ1AK1

AK14AK15

AJ16

AK16

AF16

AK11AK10

AK9AJ10AH10

AH16

AJ2

AK25AK24

AH22AJ22

AG18

AK23AK22

AF18

C6

AK17AJ25AH25

AF24AG24

U7D1

360PF10%50V

NPO

360PF10%

603

50V

NPO603

CPU_PWRGD_V1P1_N

FSB_CLK_DP

X02046-002

IC1 OF 10

CPU_SPI_SI

1%6.19K

XENON_FABK

V_GPUCORE

V_MEM

V_GPUCORE

V_GPUCORE

V_MEM

V_MEM

V_MEM

V_GPUCORE

V_GPUCORE

V_MEM

402

10K

10K5%EMPTY402

10K

CH5%10K

402

SMT

1206EMPTY

5.11K

CPU_VREG_APS4CPU_VREG_APS5

10%6.3VX5R402

CPU_SPI_SI_R

EMPTY5%10K

402

CPU_SPI_SI

CH402

5%100

CPU_SYS_CONFIG1

CPU_PULSE_LIMIT_BYPASS

CPU_TRIGGER_IN

CPU_RST_V1P1_N

CPU_SPI_EN

CPU_SPI_SO_R

CPU_VREG_APS2

CPU_SPI_SO

CPU_FSB_CLK_SEL

CPU_PLL_BYPASS

CPU_RST_N

FSB_CLK_DN

CPU_ANL_1

CPU_FSB_IMPED_CAL_DPCPU_FSB_IMPED_CAL_DN

CPU_SPI_EN_R

CPU_SPI_CLK_R

CPU_VREG_APS3

CPU_VDDS1_DNCPU_VDDS1_DP

CPU_PWRGD

CPU_SPARE1

CPU_PSRO0_OUT

CPU_VDDS0_DN

VREG_EFUSE_EN

CPU_TEST_EN

CPU_SPI_SO

CPU_ANL_1_R

CPU_SPI_EN

CPU_TEMP_P

CPU_FSB_HF_CLKOUT_DNCPU_FSB_HF_CLKOUT_DP

CPU_RES0_DP

CPU_VDDS0_DP

CPU_RES0_DN

CPU_SPI_WP_N

CPU_CORE_IF_BGR_PLL

CPU_SPI_CLK

CPU_ANL_2

CPU_SPARE0

CPU_SPI_WP_N

CH402

5%

EMPTY

10K

402

5%

5%10K402

402

5%CH

CH

1.07K1%

402

402CH

10K5%

402

10K5%

5%CH402

1K

01234

EMPTY5%

402

10K

SMT

CH5%10K

402

CH402

10UF

6.3V10%

EMPTY4021%

0

EMPTY402

5%EMPTY5%0

10K5%CH402

CH402

CH4023.92K 1%

6.19K402 CH

1%

4021%CH

3.92K

10K

402CH5%

402CH1%931

TP

SMT

SMT

SMT

SMT

402CH5%10K

4021K 5%

CH

CH5%

4021K

CH5%

4021K

5%40210K

EMPTY

CH5%

40210K

.1UF

CH5%

4021K

CH1K 5%

402

402CH5%

10K5%

402EMPTY

402

10K5%

402EMPTY

5%

402

10K

EMPTY402

5%10K

EMPTY

402CH

10K5%

402

5%CH

10K

402CH

10K

402

5%

402

10K

CH5%

43210

43210

IC

X800552-001

SMT

EMPTY5%10K

10K

CPU_POST_IN<0..4>

CPU_SYS_CONFIG0CH

EMPTY5%10K

CH5%10K

CPU_CLK_DN

CPU_CLK_DP

CPU_SPI_SI

CPU_TEMP_N

CPU_SPI_CLK

CPU_VREG_APS0CPU_VREG_APS1

EMPTY

CPU_EXT_CLK_EN

PAGEMICROSOFT REV

CONFIDENTIAL

PROJECT NAMEDRAWING

OUTOUTOUTOUTOUT

OUT

FTP

FTPFTPFTPFTPFTP

PROBE

OUT

FTP

FTPFTP

FTPFTP

FTP

FTP

OUTOUT

IN

IN

PROBE

PROBE

PROBE

PROBE

IN

OUTOUT

2X3HDR

IN

IN

IN

OUT

AT25020A

GND

SDO

VCC

WP_N*CS_N*HOLD_N*

SDISCK

CPU VERSION 20

CORE_CLK_DPCORE_CLK_DN

HARD_RESET_BPOWER_GOOD

FSB_CLK_DPFSB_CLK_DN

FSB_CLK_SEL

PULSE_LIMIT_BYPASS

TRIGGER_IN

PSRO0_OUTPOST_IN1

EXT_CLK_EN

VDDS0_DP

FSB_IMPED_CAL_DN

RESISTOR0_DP

SYS_CONFIG0SYS_CONFIG1

PLL_BYPASS

CORE_IF_BGR_PLL

EFU_POWERON

VID1VID2VID3VID4VID5

VID0

SPI_ENSPI_CLK

TE

TEMP_PTEMP_N

SPI_SI

POST_IN0

POST_IN2

POST_IN4POST_IN3

SPI_SO

ANL_1ANL_2

SPARE1SPARE0

FSB_HF_CLKOUT_DPFSB_HF_CLKOUT_DN

FSB_IMPED_CAL_DP

RESISTOR0_DN

VDDS1_DNVDDS1_DP

VDDS0_DN

PROBE

PROBE

OUT

OUT

OUTOUT

OUTIN

OUTIN

IN

IN

CPU, FSB

[PAGE_TITLE=CPU, FSB] K75/73XENON_RETAIL

12

12

12

1212

12

12

12

121212

12

12

12

12

12

1212

12

12

12

12

12

12

1212

1212121212121212

1212

121212

12

12

12

12

12

12

12

121212

12

1212

1212 12

12

12

12

1212

12 12

12 1212

12

12

12

12

12

12

12

12

12

12

12

12

12

12

12

Wed Aug 24 09:27:01 2005

2

1 C6R6

2

1 C6T32

2

1 C6T33

2

1 C6T27

2

1 C6R14

2

1 C6R25

2

1 C6R37

2

1 C6T19

2

1 C6T7

L28L27

K29K30

J30J29

J28J27

H29H30

G28G27

F29F30

E30E29

E28E27

G30G29

AD29AD30

AC29AC30

AB30AB29

AB28AB27

AA29AA30

Y28Y27

W29W30

V30V29

V28V27

Y30Y29

U30U29

U27U28

T30T29

R30R29

R27R28

N30N29

N27N28

M30M29

L30L29

P30P29

AK27AK28

AK30AK29

AJ29AJ30

AH27AH28

AH30AH29

AF27AF28

AF30AF29

AE29AE30

AD28AD27

AG29AG30

U7D1

X02046-002

IC2 OF 10

XENON_FABK

FSB_CP_GP0_DATA0_DP

FSB_CP_GP0_CLK_DN

FSB_CP_GP1_DATA0_DP

FSB_CP_GP1_FLAG_DNFSB_CP_GP1_FLAG_DP

FSB_GP_CP0_DATA7_DN

FSB_GP_CP1_FLAG_DN

FSB_GP_CP1_DATA5_DP

FSB_GP_CP1_DATA1_DPFSB_GP_CP1_DATA0_DNFSB_GP_CP1_DATA0_DP

FSB_GP_CP1_DATA3_DN

FSB_GP_CP1_DATA4_DN

FSB_GP_CP1_DATA7_DP

FSB_GP_CP1_CLK_DP

FSB_GP_CP0_DATA6_DP

FSB_CP_GP1_DATA6_DPFSB_GP_CP1_DATA6_DN

FSB_GP_CP1_CLK_DN

FSB_CP_GP0_DATA3_DN

FSB_CP_GP0_DATA0_DN

FSB_GP_CP0_DATA2_DP

FSB_GP_CP1_DATA1_DN

FSB_GP_CP1_DATA3_DP

FSB_CP_GP0_FLAG_DPFSB_CP_GP0_FLAG_DN

FSB_CP_GP0_DATA4_DPFSB_CP_GP0_DATA4_DNFSB_CP_GP0_DATA5_DPFSB_CP_GP0_DATA5_DNFSB_CP_GP0_DATA6_DPFSB_CP_GP0_DATA6_DNFSB_CP_GP0_DATA7_DPFSB_CP_GP0_DATA7_DN

FSB_CP_GP1_CLK_DPFSB_CP_GP1_CLK_DN

FSB_CP_GP1_DATA0_DNFSB_CP_GP1_DATA1_DPFSB_CP_GP1_DATA1_DN

FSB_CP_GP1_DATA3_DN

FSB_CP_GP1_DATA5_DP

FSB_GP_CP0_FLAG_DN

FSB_GP_CP0_DATA7_DP

FSB_CP_GP0_DATA2_DP

FSB_GP_CP0_DATA4_DP

FSB_GP_CP0_DATA5_DP

FSB_CP_GP1_DATA7_DNFSB_CP_GP1_DATA7_DPFSB_CP_GP1_DATA6_DN

FSB_CP_GP1_DATA5_DN

FSB_CP_GP1_DATA4_DNFSB_CP_GP1_DATA4_DP

FSB_CP_GP1_DATA2_DNFSB_GP_CP1_DATA2_DP FSB_CP_GP1_DATA2_DP

FSB_GP_CP1_FLAG_DP

FSB_GP_CP0_DATA6_DN

FSB_GP_CP0_DATA5_DN

FSB_GP_CP0_DATA3_DNFSB_CP_GP0_DATA3_DP

FSB_GP_CP0_DATA2_DN FSB_CP_GP0_DATA2_DN

FSB_GP_CP0_DATA1_DN FSB_CP_GP0_DATA1_DNFSB_CP_GP0_DATA1_DP

FSB_GP_CP0_DATA0_DP

FSB_GP_CP0_FLAG_DP

FSB_GP_CP0_CLK_DP

FSB_GP_CP0_DATA1_DP

FSB_GP_CP0_DATA4_DN

FSB_GP_CP1_DATA2_DN

FSB_GP_CP1_DATA4_DP

FSB_GP_CP1_DATA6_DP

FSB_GP_CP1_DATA7_DN

FSB_GP_CP0_CLK_DN

FSB_GP_CP0_DATA0_DN

FSB_GP_CP0_DATA3_DP

FSB_CP_GP0_CLK_DP

FSB_GP_CP1_DATA5_DN

FSB_CP_GP1_DATA3_DP

402X5R6.3V10%.1UF

402

.1UF10%6.3VX5R

402X5R6.3V10%.1UF

402

.1UF10%6.3VX5R

402X5R6.3V10%.1UF

V_GPUCORE

X5R

.1UF10%6.3V

402

.1UF

X5R6.3V10%

402

6.3V10%.1UF

402X5R

.1UF

X5R6.3V10%

402

PAGEMICROSOFT REV

CONFIDENTIAL

PROJECT NAMEDRAWING

OUT

INININ

ININ

ININ

OUT

IN

ININ

ININININININ

IN

OUT

IN

ININ

IN

ININININ

IN

IN

OUT

INININ

IN

ININININ

IN

IN

OUT

IN

ININ

CPU VERSION 20

GP_CP0_DATA5_DPGP_CP0_DATA4_DNGP_CP0_DATA4_DP

CP_GP0_DATA2_DP

CP_GP0_DATA1_DP

GP_CP0_DATA7_DPGP_CP0_DATA7_DN

GP_CP1_CLK_DPGP_CP1_CLK_DN

GP_CP1_FLAG_DPGP_CP1_FLAG_DN

GP_CP1_DATA0_DP

GP_CP0_DATA0_DNGP_CP0_DATA0_DP

GP_CP0_FLAG_DNGP_CP0_FLAG_DP

GP_CP0_CLK_DNGP_CP0_CLK_DP

GP_CP0_DATA5_DNGP_CP0_DATA6_DPGP_CP0_DATA6_DN

CP_GP1_DATA7_DNCP_GP1_DATA7_DPCP_GP1_DATA6_DNCP_GP1_DATA6_DPCP_GP1_DATA5_DNCP_GP1_DATA5_DPCP_GP1_DATA4_DNCP_GP1_DATA4_DPCP_GP1_DATA3_DNCP_GP1_DATA3_DPCP_GP1_DATA2_DNCP_GP1_DATA2_DPCP_GP1_DATA1_DNCP_GP1_DATA1_DPCP_GP1_DATA0_DNCP_GP1_DATA0_DP

CP_GP1_FLAG_DNCP_GP1_FLAG_DP

CP_GP1_CLK_DNCP_GP1_CLK_DP

CP_GP0_DATA7_DNCP_GP0_DATA7_DPCP_GP0_DATA6_DNCP_GP0_DATA6_DPCP_GP0_DATA5_DNCP_GP0_DATA5_DPCP_GP0_DATA4_DNCP_GP0_DATA4_DP

CP_GP0_FLAG_DNCP_GP0_FLAG_DP

CP_GP0_CLK_DNCP_GP0_CLK_DP

GP_CP1_DATA7_DNGP_CP1_DATA7_DPGP_CP1_DATA6_DNGP_CP1_DATA6_DPGP_CP1_DATA5_DNGP_CP1_DATA5_DPGP_CP1_DATA4_DNGP_CP1_DATA4_DPGP_CP1_DATA3_DNGP_CP1_DATA3_DPGP_CP1_DATA2_DNGP_CP1_DATA2_DPGP_CP1_DATA1_DNGP_CP1_DATA1_DPGP_CP1_DATA0_DN

GP_CP0_DATA3_DNGP_CP0_DATA3_DPGP_CP0_DATA2_DNGP_CP0_DATA2_DPGP_CP0_DATA1_DNGP_CP0_DATA1_DP

CP_GP0_DATA0_DPCP_GP0_DATA0_DN

CP_GP0_DATA1_DN

CP_GP0_DATA2_DNCP_GP0_DATA3_DPCP_GP0_DATA3_DN

OUT

OUT

OUTOUTOUTOUTOUT

OUTOUT

OUTOUTOUT

OUT

OUTOUT

OUTOUTOUT

OUTOUT

OUTOUT

OUT

OUT

OUTOUT

OUTOUT

OUTOUTOUT

OUTOUT

OUT

OUT

CPU, FSB POWER + PLL POWER

[PAGE_TITLE=CPU, FSB POWER + PLL POWER] K76/73XENON_RETAILWed Aug 24 09:27:01 2005

2

1C7R116

2

1C7R115

2

1C7R114

2 1R7T2

2

1 C7D1

21ST7D1

21FB7D1

2

1C6R3

21ST6R2

21FB6R2

2

1 C6R2

21ST6R1

21FB6R1

2

1C6D1

21ST6D1

21FB6D1

21ST7R1

2

1 C7R1

21FB7R1

2

1 C7D2

2

1C6R5

2

1 C6R4

2

1C6D4 B6

A6

AK13

AK6

AK26AJ27AH26AG27AF26

Y26W27V26U26T27R26P27

AE27

N26M27L26K27J26H27G26F27E26D29

AD26

D27D25D21D17D13D10C26C23C20C17

AC27

C14C11C8B27B24B21B18B15B12B9

AB26AA27

AJ13

AF20AG20

AF22AG22

AK19AK18

AJ19AH19

U7D1

2

1 C7R7

X02046-002

IC4 of 10

XENON_FABK

6.3V

CPU_VDDE

V_CPU_FSB_HF_VDDA_PLL

V_CPU_CORE_HF_VDDA_PLL

V_CPU_CORE_HF_GNDA_PLL

V_CPU_CORE_IF_VDDA_PLL

V_CPU_CORE_IF_GNDA_PLL

V_CPU_FSB_HF_GNDA_PLL

V_CPU_FSB_IF_VDDA_PLL

V_CPU_FSB_IF_GNDA_PLL

V_CPU_VDDA_RNG

V_CPU_GNDA_RNG

2.2UF

603X5R6.3V10%

10%6.3V

603X5R

2.2UF

6.3V

603X5R

10%2.2UF

X5R6.3V10%2.2UF

603

2.2UF

603X5R6.3V10%

.1UF

X5R402

6.3V10%

6.3V

.1UF

402X5R

10% 10%

402X5R

.1UF

V_1P8

10KCH5%

402

1UF

603

10%50VEMPTY

V_EFUSE

1K FB603

0.7DCR0.2A

.1UF

402

10%

X5R6.3V

FB1K603

0.7DCR0.2A

402

.1UF10%6.3VX5R

603FB1K

0.7DCR0.2A

10%.1UF

6.3VX5R402

603FB1K

0.7DCR0.2A

402X5R6.3V

.1UF10%

0.7DCR0.2A

FB603

1K

V_CPUPLL V_GPUCORE

PAGEMICROSOFT REV

CONFIDENTIAL

PROJECT NAMEDRAWING

CPU VERSION 20

VDD_IO

VDDEVDDE_SEC

CORE_HF_VDDA_PLLCORE_HF_GNDA_PLL

CORE_IF_VDDA_PLLCORE_IF_GNDA_PLL

FSB_HF_VDDA_PLLFSB_HF_GNDA_PLL

FSB_IF_VDDA_PLLFSB_IF_GNDA_PLL

VDDA_RNGGNDA_RNG

VDD_FSB0VDD_FSB1VDD_FSB2VDD_FSB3VDD_FSB4VDD_FSB5VDD_FSB6VDD_FSB7VDD_FSB8VDD_FSB9

VDD_FSB10VDD_FSB11VDD_FSB12VDD_FSB13VDD_FSB14VDD_FSB15VDD_FSB16VDD_FSB17VDD_FSB18VDD_FSB19VDD_FSB20VDD_FSB21VDD_FSB22VDD_FSB23VDD_FSB24VDD_FSB25VDD_FSB26VDD_FSB27VDD_FSB28VDD_FSB29VDD_FSB30VDD_FSB31VDD_FSB32VDD_FSB33VDD_FSB34VDD_FSB35VDD_FSB36VDD_FSB37VDD_FSB38VDD_FSB39VDD_FSB40VDD_FSB41VDD_FSB42VDD_FSB43VDD_FSB44VDD_FSB45VDD_FSB46

SHORT

SHORT

SHORT

SHORT

SHORT

CPU, CORE POWER

[PAGE_TITLE=CPU, CORE POWER] K77/73XENON_RETAILWed Aug 24 09:27:01 2005

Y25Y23Y21Y19Y17Y15Y13Y11Y9Y7Y5Y3Y1W24W22W20W18W16W14W12W10W8W6W4W2V25V23V21V19V17V15V13V11V9V7V5V3V1U24U22U20U18U16U14U12U10U8

U6U4U2

T25T23T21T19T17T15T13T11

T9T7T5T3T1

R24R22R20R18R16R14R12R10

R8R6R4R2

P25P23P21P19P17P15P13P11

P9P7P5P3P1

N24N22N20N18N16N14

U7D1

E4E2D9D7

N12N10N8N6N4N2M25M23M21M19M17M15M13M11M9M7M5M3M1L24L22L20L18L16L14L12L10L8L6L4L2K25K23K21K19K17K15K13K11K9K7K5K3K1J24J22J20

J18J16J14J12J10

J8J6J4J2

H25H23H21H19H17H15H13H11

H9H7H5H3H1

G24G22G20G18G16G14G12G10

G8G6G4G2

F11F9F7F5F3F1

E10E8E6

U7D1

D5D3D1C2B1AJ14

AA20

AJ11AJ8AJ5AH15AH12AH9AH6AH3AG14AG12

AA18

AG10AG8AG6AG4AG2AF25AF23AF21AF19AF17

AA16

AF15AF13AF11AF9AF7AF5AF3AF1AE24AE22

AA14

AE20AE18AE16AE14AE12AE10AE8AE6AE4AE2

AA12

AD25AD23

AD21AD19AD17AD15AD13AD11

AD9AD7

AA10

AD5AD3AD1

AC24AC22AC20AC18AC16AC14AC12

AA8

AC10AC8AC6AC4AC2

AB25AB23AB21AB19AB17

AA6

AB15AB13AB11

AB9AB7AB5AB3AB1

AA24AA22

AA4AA2

U7D1

X02046-002

IC7 of 10

X02046-002

IC6 of 10

X02046-002

IC5 of 10

XENON_FABK

V_CPUCOREV_CPUCOREV_CPUCORE V_CPUCORE V_CPUCOREV_CPUCORE

PAGEMICROSOFT REV

CONFIDENTIAL

PROJECT NAMEDRAWING

CPU VERSION 20

VDD51VDD50VDD49

VDD10VDD11VDD12VDD13

VDD41VDD40

VDD42VDD43

VDD45

VDD58

VDD56VDD57

VDD59

VDD73VDD72

VDD93VDD94VDD95

VDD88VDD89VDD90VDD91VDD92

VDD83VDD84VDD85VDD86VDD87

VDD82

VDD78VDD79VDD80VDD81

VDD77

VDD74VDD75VDD76

VDD67VDD68VDD69VDD70VDD71

VDD62VDD63VDD64VDD65VDD66

VDD60VDD61

VDD52VDD53VDD54VDD55

VDD48

VDD2VDD1VDD0

VDD7

VDD9VDD8

VDD6

VDD46VDD47

VDD44

VDD35VDD36VDD37VDD38VDD39

VDD34

VDD30VDD31VDD32VDD33

VDD29

VDD25VDD26VDD27VDD28

VDD24

VDD19VDD20VDD21VDD22VDD23

VDD14VDD15VDD16VDD17VDD18

VDD4VDD5

VDD3

CPU VERSION 20

VDD237

VDD197VDD196

VDD193VDD194VDD195

VDD202VDD201

VDD198

VDD207

VDD204VDD203

VDD205VDD206

VDD212

VDD208VDD209VDD210VDD211

VDD213

VDD217

VDD214VDD215VDD216

VDD218

VDD222

VDD219VDD220VDD221

VDD223

VDD228VDD227

VDD224VDD225VDD226

VDD233VDD232

VDD229VDD230VDD231

VDD234VDD235VDD236

VDD192VDD191VDD190

VDD199VDD200

VDD244VDD243

VDD240VDD241VDD242

VDD249VDD248

VDD245VDD246VDD247

VDD254

VDD251VDD250

VDD252VDD253

VDD259

VDD255VDD256VDD257VDD258

VDD260

VDD264

VDD261VDD262VDD263

VDD265

VDD269

VDD266VDD267VDD268

VDD270

VDD275VDD274

VDD271VDD272VDD273

VDD280VDD279

VDD276VDD277VDD278

VDD281VDD282VDD283

VDD239VDD238

CPU VERSION 20

VDD146VDD145

VDD96VDD97VDD98VDD99

VDD104VDD105VDD106

VDD143

VDD147VDD148VDD149VDD150VDD151

VDD168

VDD189VDD188VDD187

VDD184VDD183VDD182

VDD185VDD186

VDD179VDD178VDD177

VDD180VDD181

VDD176

VDD174VDD173VDD172

VDD175

VDD171

VDD169

VDD167

VDD170

VDD166

VDD164VDD163VDD162VDD161

VDD165

VDD159VDD158

VDD156VDD157

VDD160

VDD153VDD152

VDD154VDD155

VDD144

VDD142VDD141VDD140

VDD137VDD136VDD135

VDD138VDD139

VDD132VDD131VDD130

VDD133VDD134

VDD129

VDD127VDD126VDD125

VDD128

VDD124

VDD122VDD121VDD120

VDD123

VDD119

VDD117VDD116VDD115VDD114

VDD118

VDD112VDD111

VDD109VDD110

VDD113

VDD107VDD108

VDD101VDD100

VDD102VDD103

CPU, POWER

[PAGE_TITLE=CPU, POWER] K78/73XENON_RETAILWed Aug 24 09:27:02 2005

Y24Y22Y20Y18Y16Y14Y12Y10Y8Y6Y4Y2W28W26W25W23W21W19W17W15W13W11W9W7W5W3W1V24V22V20V18V16V14V12V10V8V6V4V2U25U23U21U19U17U15U13U11U9U7U5U3U1T28T26T24T22T20T18

T16T14T12T10

T8T6T4T2

R25R23R21R19R17R15R13R11

R9R7R5R3R1

P28P26P24P22P20P18P16P14P12P10

P8P6P4P2

N25N23N21N19N17N15N13N11

N9N7N5N3N1

M28M26M24M22M20M18M16M14M12M10

U7D1

M8M6M4M2L25L23L21L19L17L15L13L11L9L7L5L3L1K28K26K24K22K20K18K16K14K12K10K8K6K4K2J25J23J21J19J17J15J13J11J9J7J5J3J1H28H26H24H22H20H18H16H14H12H10H8H6H4H2

G25G23G21G19G17G15G13G11

G9G7G5G3G1

F28F26F24F22F20F18F16F14F12F10

F8F6F4F2E9E7E5E3E1

D30D28D26D23D19D15D11

D8D6D4D2

C27C24C21C18C15C12

C9C3C1

B29B26B23B20B17B14

U7D1

AH21AH20AH18AH17AH14AH11AH8AH5AH2AG28

AA19

AG26AG25AG23AG21AG19AG17AG15AG13AG11AG9

AA17

AG7AG5AG3AG1AF14AF12AF10AF8AF6AF4

AA15

AF2AE28AE26AE25AE23AE21AE19AE17AE15AE13

AA13

AE11AE9

AE7AE5AE3AE1

AD24AD22AD20AD18

AA11

AD16AD14AD12AD10

AD8AD6AD4AD2

AC28AC26

AA9

AC25AC23AC21AC19AC17AC15AC13AC11

AC9AC7

AA7

AC5AC3AC1

AB24AB22AB20AB18AB16AB14AB12

AA5

AB10AB8AB6AB4AB2

AA28AA26AA25

B11B8AJ28AJ26AJ24AJ23AJ21

AA23

AJ20AJ18AJ17AJ15AJ12AJ9AJ6AJ3AH24AH23

AA21

AA3AA1

U7D1

X02046-002

IC10 of 10

X02046-002

IC9 of 10

X02046-002

IC8 of 10

XENON_FABK PAGEMICROSOFT REV

CONFIDENTIAL

PROJECT NAMEDRAWING

CPU VERSION 20

VSS117VSS118

VSS175

VSS123VSS124VSS125VSS126VSS127VSS128VSS129

VSS131

VSS133VSS134

VSS136

VSS216VSS217VSS218VSS219VSS220VSS221VSS222VSS223VSS224

VSS207VSS206

VSS232VSS231VSS230

VSS227

VSS225VSS226

VSS228VSS229

VSS215VSS214

VSS212VSS211VSS210

VSS213

VSS209

VSS205

VSS208

VSS204

VSS202VSS201VSS200VSS199

VSS203

VSS197VSS196

VSS194VSS195

VSS198

VSS191VSS190VSS189

VSS192VSS193

VSS186VSS185VSS184

VSS187VSS188

VSS181VSS180VSS179

VSS182VSS183

VSS178VSS177VSS176

VSS174VSS173VSS172

VSS169

VSS167VSS168

VSS170VSS171

VSS164VSS163VSS162

VSS165VSS166

VSS159VSS158VSS157

VSS160VSS161

VSS156

VSS154VSS153VSS152

VSS155

VSS151

VSS149VSS148VSS147

VSS150

VSS146

VSS144VSS143VSS142VSS141

VSS145

VSS139VSS138VSS137

VSS140

VSS132

VSS135

VSS130

VSS122VSS121VSS120VSS119

CPU VERSION 20

VSS286VSS287VSS288VSS289

VSS291VSS292VSS293

VSS335VSS334VSS333

VSS331VSS330VSS329VSS328

VSS322VSS323

VSS348VSS347VSS346

VSS343

VSS341VSS342

VSS344VSS345

VSS338VSS337VSS336

VSS339VSS340

VSS332

VSS327VSS326VSS325

VSS321

VSS324

VSS320

VSS318VSS317VSS316VSS315

VSS319

VSS313VSS312

VSS310VSS311

VSS314

VSS307VSS306VSS305

VSS308VSS309

VSS302VSS301VSS300

VSS303VSS304

VSS297VSS296VSS295

VSS298VSS299

VSS294

VSS257VSS258

VSS290

VSS285

VSS283VSS284

VSS280VSS279VSS278

VSS281VSS282

VSS275VSS274VSS273

VSS276VSS277

VSS272

VSS270VSS269VSS268

VSS271

VSS267

VSS265VSS264VSS263

VSS266

VSS262

VSS260VSS259

VSS261

VSS255VSS254

VSS252VSS253

VSS256

VSS249VSS248VSS247

VSS250VSS251

VSS244VSS243VSS242

VSS245VSS246

VSS239VSS238VSS237

VSS240VSS241

VSS236VSS235

VSS233VSS234

CPU VERSION 20

VSS58VSS0

VSS113VSS114

VSS116VSS115

VSS109VSS108

VSS110VSS111VSS112

VSS103VSS104VSS105VSS106VSS107

VSS98VSS99

VSS100VSS101VSS102

VSS97

VSS93VSS94VSS95VSS96

VSS92

VSS88VSS89VSS90VSS91

VSS87

VSS83VSS84VSS85

VSS82

VSS86

VSS78VSS77

VSS79VSS80VSS81

VSS72VSS73VSS74VSS75VSS76

VSS67VSS68VSS69VSS70VSS71

VSS62

VSS64VSS63

VSS65VSS66

VSS59VSS60VSS61

VSS28VSS27VSS26

VSS22VSS21VSS20

VSS57VSS56VSS55

VSS52

VSS50VSS51

VSS53VSS54

VSS47VSS46VSS45

VSS48VSS49

VSS42VSS41VSS40

VSS43VSS44

VSS39

VSS37VSS36VSS35

VSS38

VSS34

VSS32VSS31VSS30

VSS33

VSS29

VSS25VSS24

VSS19

VSS23

VSS16VSS15VSS14

VSS17VSS18

VSS11VSS10VSS9

VSS12VSS13

VSS6VSS5VSS4

VSS7VSS8

VSS3VSS2VSS1

CPU, DECOUPLING

[PAGE_TITLE=CPU, DECOUPLING] K79/73XENON_RETAILWed Aug 24 09:27:03 2005

21C7T45

21C7T1

21C7R16

21C7R13

21C7R11

21C7R10

21C7R12

21C7T88

21C7T76

21C7T77

21C7T78

21C7T79

21C7D20

21C7T33

21C7R28

21C7T32

21C7E3

21C7R2

21C7T87

21C7E11

21C7E10

21C7E12

21C7D16

21C7T93

21C7T101

21C7T94

21C7D21

21C7E14

21C7E8

21C7R122

21C7R121

21C7T84

21C7D17

21C7D14

21C7E5

21C7D11

21C7T83

21C7R118

21C7D13

21C7T36

21C7D19

21C7E7

21C7R119

21C7D6

21C7R92

21C7T96

21C7R117

21C7R26

21C7E4

21C7D15

21C7R29

21C7R91

21C7E16

21C7D7

21C7D18

21C7R120

21C7D3

21C7T95

21C7R93

21C7D5

21C7D12

21C7E6

21C7T85

21C7E1

21C7R94

21C7R6

21C7T34

21C7R5

21C7D9

21C7D4

21C7D8

21C7R27

21C7T35

21C7R4

21C7D10

21C7D22

21C7T97

21C7T86

21C7E9

21C7E15

21C7E2

21C7R90

21C7R30

21C7R3

XENON_FABK

X5R

10%6.3V

402

.1UF

X5R

10%6.3V

.1UF

402

X5R

10%6.3V

402

.1UF

X5R

10%6.3V

.1UF

402

X5R

10%6.3V

.1UF

402

X5R

10%6.3V

402

.1UF

X5R

10%6.3V

.1UF

402

X5R

10%6.3V

.1UF

402

V_CPUCORE

805X5R

6.3V10%4.7UF

805X5R

6.3V10%4.7UF

805X5R

6.3V10%4.7UF

805X5R

6.3V10%4.7UF

805X5R

6.3V10%4.7UF

805X5R

6.3V10%4.7UF

805X5R

6.3V10%4.7UF

805X5R

6.3V10%4.7UF

805X5R

6.3V10%4.7UF

805X5R

6.3V10%4.7UF

805X5R

6.3V10%4.7UF

805X5R

6.3V10%4.7UF

805X5R

6.3V10%4.7UF

805X5R

6.3V10%4.7UF

805X5R

6.3V10%4.7UF

805X5R

6.3V10%4.7UF

805X5R

6.3V10%4.7UF

V_CPUCORE

805X5R

6.3V10%4.7UF

805X5R

6.3V10%4.7UF

805X5R

6.3V10%4.7UF

805X5R

6.3V10%4.7UF

805X5R

6.3V10%4.7UF

805X5R

6.3V10%4.7UF

805X5R

6.3V10%4.7UF

805X5R

6.3V10%4.7UF

805X5R

6.3V10%4.7UF

805X5R

6.3V10%4.7UF

805X5R

6.3V10%4.7UF

805X5R

6.3V10%4.7UF

805X5R

6.3V10%4.7UF

805X5R

6.3V10%4.7UF

805X5R

6.3V10%4.7UF

805X5R

6.3V10%4.7UF

805X5R

6.3V10%4.7UF

805X5R

6.3V10%4.7UF

805X5R

6.3V10%4.7UF

805X5R

6.3V10%4.7UF

805X5R

6.3V10%4.7UF

805X5R

6.3V10%4.7UF

805X5R

6.3V10%4.7UF

805X5R

6.3V10%4.7UF

805X5R

6.3V10%4.7UF

805X5R

6.3V10%4.7UF

805X5R

6.3V10%4.7UF

805X5R

6.3V10%4.7UF

805X5R

6.3V10%4.7UF

805X5R

6.3V10%4.7UF

805X5R

6.3V10%4.7UF

805X5R

6.3V10%4.7UF

805X5R

6.3V10%4.7UF

805X5R

6.3V10%4.7UF

805X5R

6.3V10%4.7UF

805X5R

6.3V10%4.7UF

805X5R

6.3V10%4.7UF

805X5R

6.3V10%4.7UF

805X5R

6.3V10%4.7UF

805X5R

6.3V10%4.7UF

805X5R

6.3V10%4.7UF

805X5R

6.3V10%4.7UF

805X5R

6.3V10%4.7UF

805X5R

6.3V10%4.7UF

805X5R

6.3V10%4.7UF

805X5R

6.3V10%4.7UF

805X5R

6.3V10%4.7UF

805X5R

6.3V10%4.7UF

805X5R

6.3V10%4.7UF

805X5R

6.3V10%4.7UF

805X5R

6.3V10%4.7UF

805X5R

6.3V10%4.7UF

805X5R

6.3V10%4.7UF

X5R

10%6.3V

402

.1UF

X5R

10%6.3V

402

.1UF

X5R

10%6.3V

402

.1UF

X5R

10%6.3V

.1UF

402805X5R

6.3V10%4.7UF

805X5R

6.3V10%4.7UF

DRAWINGPAGEMICROSOFT REV

CONFIDENTIAL

PROJECT NAME

CPU SOCKET

CPU, DECOUPLING

N: EMPTY FOR

[PAGE_TITLE=CPU, DECOUPLING] K710/73XENON_RETAILWed Aug 24 09:27:03 2005

21C7T8

21C7T20

21C7R48

21C7T82

21C7T81

21C7T71

21C7T72

21C7T73

21C7T74

21C7T75

21C7T70

21C7T69

21C7R46

21C6R11

21C7R45

21C6R17

21C7R44

21C7R37

21C7R38

21C7R25

21C7R24

21C7R23

21C7R77

21C7R79

21C7R63

21C7R47

21C7R53

21C7R70

21C7R84

21C7R71

21C7R54

21C7R61

21C6T26

21C6R21

21C7R64

21C7T15

21C7R76

21C6R19

21C6R16

21C7R43

21C6R27

21C6R28

21C6R29

21C7R19

21C7R34

21C7R35

21C6R20

21C7R57

21C7R69

21C7R68

21C6T5

21C6R31

21C7R22

21C7R36

21C7R78

21C7R62

21C7R72

21C7R49

21C7R55

21C7T9

21C6R32

21C7R80

21C6R30

21C7R60

21C6T23

21C7R99

21C7R74

21C7R100

21C7R58

21C7R59

21C6R23

21C6R22

21C7R50

21C6T6

21C6T25

21C7R89

21C7T37

21C7R88

21C6R36

21C7R81

21C6T4

21C7T27

21C7R102

21C6R43

21C6T1

21C6R18

21C6R39

21C6R34

21C6R38

21C7T10

21C6R35

21C7T2

21C7R110

21C7R111

21C7R66

21C6R40

21C6R45

21C7T5

21C7T3

21C7R67

21C6R42

21C7R51

21C7R52

21C7T22

21C6T2

21C6R44

21C7T19

21C6T10

21C6R33

21C7T21

XENON_FABK

6.3V.1UF 10%

X5R

402

6.3VX5R

.1UF 10%

X5R402

.1UF 10%6.3V

10%.1UF6.3VX5R402

X5R402

.1UF 10%6.3V

6.3VX5R402

.1UF

6.3V

402

10%

X5R

.1UF

6.3VX5R402

.1UF 10%

10%.1UF6.3VX5R402

6.3VX5R402

.1UF 10%

6.3VX5R402

.1UF 10%

6.3VX5R402

.1UF 10%

6.3V.1UF

402X5R

10%

6.3VX5R402

.1UF 10%

.1UF 10%6.3VX5R402

10%6.3VX5R402

.1UF

.1UF 10%6.3VX5R402

.1UF 10%6.3VX5R402

X5R402

6.3V.1UF 10%

402X5R

6.3V.1UF 10%

402

6.3V.1UF 10%

X5R

.1UF

402X5R

10%

X5R6.3V

.1UF 10%

X5R6.3V

10%.1UF

402

.1UF 10%

X5R402

6.3V

402

10%6.3VX5R402

.1UF

402

6.3VX5R

10%6.3VX5R402

.1UF

402

.1UF 10%

X5R6.3V

402X5R

10%

6.3VX5R

.1UF 10%

402

10%

X5R402

.1UF

.1UF6.3VX5R402

10%

6.3VX5R

.1UF 10%

402

6.3VX5R402

.1UF 10%

6.3VX5R402

.1UF 10%

6.3VX5R402

.1UF 10%

.1UF6.3VX5R

10%

6.3VX5R402

.1UF 10%

402

6.3V.1UF

X5R

10%

10%

X5R6.3V

402

.1UF

.1UF6.3V

402X5R

10%

6.3VX5R

.1UF 10%

402

X5R402

6.3V.1UF 10%

402

10%

X5R6.3V

.1UF

6.3VX5R

.1UF 10%

402

6.3VX5R

.1UF 10%

402

X5R402

10%6.3V

.1UF

X5R

.1UF 10%6.3V

402

6.3VX5R402

10%.1UF

6.3VX5R

.1UF 10%

402

10%

402X5R

6.3V

6.3VX5R402

.1UF 10%

6.3VX5R

.1UF 10%

402

.1UF

X5R402

6.3V10%

6.3VX5R402

10%.1UF

6.3VX5R402

.1UF 10%

402X5R

.1UF

.1UF 10%6.3VX5R402

6.3VX5R402

.1UF 10%

6.3VX5R402

.1UF 10%

6.3VX5R402

.1UF 10%

X5R402

.1UF 10%6.3V

.1UF6.3V

10%

X5R402

6.3VX5R402

.1UF 10%

.1UF 10%6.3V

402

.1UF

402

10%

X5R6.3V

6.3VX5R402

.1UF 10%

6.3VX5R402

.1UF 10%

.1UF6.3VX5R402

.1UF6.3VX5R402

6.3VX5R402

.1UF 10%

6.3VX5R402

.1UF 10%

V_CPUCORE

6.3VX5R402

.1UF 10%

X5R402

.1UF6.3V

10%

6.3VX5R

.1UF 10%

6.3VX5R402

.1UF 10%

6.3VX5R402

.1UF 10%

X5R402

.1UF 10%6.3V

X5R

.1UF6.3V

402

10%

.1UF 10%6.3V

402X5R

.1UF 10%6.3VX5R402

6.3VX5R402

.1UF 10%

6.3VX5R402

.1UF 10%

6.3VX5R

.1UF 10%

6.3VX5R

.1UF 10%

402

402

10%6.3VX5R

.1UF

6.3VX5R

10%

402

.1UF

.1UF 10%6.3VX5R402

6.3VX5R402

.1UF 10%

6.3VX5R402

10%.1UF

X5R402

.1UF 10%6.3V

.1UF6.3VX5R402

10%

402X5R

.1UF 10%

.1UF 10%6.3VX5R402

.1UF6.3V

10%

402

6.3V10%

X5R402

.1UF

6.3VX5R

.1UF 10%

402

6.3VX5R402

.1UF 10%

.1UF 10%6.3VX5R402

10%.1UF6.3VX5R402

6.3VX5R402

.1UF 10%

X5R402

6.3V.1UF

6.3V.1UF 10%

X5R402

10%

402X5R

6.3V.1UF

6.3V

6.3V

10%

402

.1UF

402

402

.1UF

402

10%10%

X5R

X5R

6.3V

402

10%

10% 10%6.3V

.1UF6.3V

.1UF 10%6.3VX5R

6.3V

402

.1UF 10%

X5R

10%

.1UF6.3V

402

10%

X5R

.1UF 10%

402

6.3VX5R

402X5R

6.3V.1UF

DRAWINGPAGEMICROSOFT REV

CONFIDENTIAL

PROJECT NAME

CPU, DECOUPLING

[PAGE_TITLE=CPU, DECOUPLING] K711/73XENON_RETAILWed Aug 24 09:27:05 2005

21C7T80

21C7R9

21C7R14

21C7R15

21C7R8

21C7T68

21C7T67

21C7T66

21C7T65

21C7T64

21C7T63

21C7T62

21C6T30

21C6T29

21C6T28

21C6R13

21C7R107

21C6R12

21C6T21

21C7R21

21C6T3

21C6T9

21C7R39

21C7R40

21C7R41

21C6R26

21C7R56

21C7R82

21C7R42

21C7R20

21C7R18

21C7T12

21C7R31

21C7R17

21C6T11

21C7R32

21C7R33

21C6R41

21C6R15

21C6R10

21C7T31

21C7T28

21C6T14

21C6T12

21C7T41

21C7T17

21C7T13

21C6T22

21C7T49

21C6T8

21C7R98

21C7T56

21C6T20

21C7R106

21C7T50

21C7R86

21C7T59

21C7R73

21C6R8

21C7T60

21C7T61

21C6R7

21C6R9

21C7T52

21C7T53

21C7R101

21C7R85

21C7R75

21C7T40

21C7T11

21C7R65

21C7T38

21C6R24

21C7T58

21C7T29

21C7T30

21C6T24

21C7T54

21C7T14

21C6T13

21C7T16

21C6T18

21C7T48

21C7T26

21C7T23

21C6T17

21C7T4

21C7R105

21C7R109

21C7T39

21C7T18

21C7T55

21C7R108

21C7R96

21C7R104

21C7T57

21C7R97

21C7T46

21C7T25

21C7T24

21C7R83

21C7T42

21C7T44

21C7T43

21C7R103

21C7R95

21C7T47

21C7T51

21C6T16

21C6T15

XENON_FABK

6.3VX5R402

.1UF 10%

6.3V

402

.1UF 10%

X5R6.3VX5R402

.1UF 10%

6.3VX5R402

.1UF 10%

X5R402

10%.1UF6.3V

.1UF 10%6.3VX5R402

.1UF

402X5R

10%6.3V

.1UF 10%6.3VX5R402

6.3VX5R402

.1UF 10%

6.3VX5R402

.1UF 10%

.1UF 10%6.3VX5R402

6.3VX5R402

.1UF 10%

6.3VX5R402

.1UF 10%

.1UF 10%

X5R402

6.3V

6.3VX5R402

.1UF 10%

6.3VX5R402

.1UF 10%

.1UF 10%6.3VX5R402

X5R

.1UF 10%6.3V

402

6.3VX5R402

.1UF 10%

X5R

.1UF 10%6.3V

402

6.3VX5R402

10%.1UF.1UF 10%6.3VX5R402

.1UF6.3VX5R402

10%

6.3VX5R402

.1UF 10%

X5R6.3V

10%.1UF

402

.1UF6.3VX5R402

10%

10%.1UF

402X5R

6.3V

X5R

10%.1UF6.3V

402

10%.1UF

402

6.3VX5R

6.3VX5R402

.1UF 10%

10%.1UF

X5R402

6.3V

.1UF 10%6.3VX5R402

402

6.3VX5R

.1UF 10%

6.3VX5R402

.1UF 10%

6.3VX5R402

.1UF 10%

10%.1UF6.3VX5R402

X5R402

.1UF 10%6.3V

6.3VX5R402

.1UF 10%

6.3VX5R402

.1UF 10%

6.3VX5R402

.1UF 10%

6.3VX5R402

.1UF 10%

6.3VX5R402

.1UF 10%

6.3VX5R

.1UF 10%

402

6.3VX5R402

.1UF 10%

.1UF 10%6.3VX5R402

X5R402

.1UF 10%6.3V

6.3VX5R402

.1UF 10%

6.3VX5R402

.1UF 10%

6.3VX5R402

.1UF 10%

6.3VX5R402

.1UF 10%

10%.1UF6.3VX5R402

402

.1UF 10%6.3VX5R

.1UF 10%6.3VX5R402

X5R402

10%.1UF6.3V

402X5R

10%6.3V

.1UF .1UF 10%

X5R402

6.3V

X5R

.1UF 10%6.3V

402

.1UF6.3VX5R402

10%

402

6.3VX5R

.1UF 10%

6.3VX5R402

.1UF 10%

6.3VX5R

.1UF 10%

402

6.3VX5R402

.1UF 10%

6.3V.1UF 10%

X5R402

6.3VX5R402

.1UF 10%

6.3VX5R402

.1UF 10%

6.3VX5R402

.1UF 10%

402

10%

X5R

.1UF6.3V

X5R402

10%6.3V

.1UF

6.3V10%.1UF

X5R402

10%6.3VX5R402

.1UF

6.3VX5R

10%

402

.1UF

.1UF 10%6.3VX5R402

6.3VX5R402

.1UF 10%

6.3VX5R402

.1UF 10%

10%6.3VX5R402

.1UF

6.3VX5R402

10%.1UF

6.3VX5R402

.1UF 10%

6.3VX5R402

.1UF 10%

6.3V10%

402X5R

.1UF

6.3VX5R402

.1UF 10%

.1UF 10%6.3VX5R402

.1UF 10%6.3VX5R402

.1UF6.3VX5R402

10%

6.3VX5R402

.1UF 10%

6.3VX5R402

.1UF 10%

6.3V

402X5R

.1UF 10%

402X5R

10%.1UF6.3V

10%

X5R402

.1UF6.3V

.1UF 10%6.3VX5R402

6.3V.1UF 10%

X5R402

6.3VX5R402

.1UF 10%

6.3VX5R402

.1UF 10%

6.3VX5R402

.1UF 10%

6.3VX5R402

.1UF 10%

6.3VX5R402

.1UF 10%

.1UF

X5R402

6.3V10%

6.3VX5R402

.1UF 10%

6.3VX5R402

.1UF 10%

6.3VX5R402

.1UF 10%

6.3VX5R

10%

402

.1UF

402X5R

.1UF 10%6.3V

6.3VX5R402

.1UF 10%

10%

X5R

.1UF

402

6.3V

6.3VX5R402

.1UF 10%

V_CPUCORE

6.3VX5R402

.1UF 10%

6.3VX5R402

.1UF 10%

6.3VX5R402

.1UF 10%

6.3VX5R402

.1UF 10%

X5R

.1UF 10%6.3V

402

X5R

.1UF 10%6.3V

402

DRAWINGPAGEMICROSOFT REV

CONFIDENTIAL

PROJECT NAME

GPU, FSB

[PAGE_TITLE=GPU, FSB]

FSB DECOUPLING

K712/73XENON_RETAIL

55555

13

5

55

55

555

5555

555

5

555

5

5

5

5

555

5

5

555

13

13 21 23 2527

13

20 22 2426

5

555

5

5

5

555

55

555

5

5

5

5

5

5

5

55

555

555555

5

5

5

5

55

5

5

55

5

20 21 2223 24 25

26 27

Wed Aug 24 09:27:06 2005

2

1

R4F8

2

1

R4U6

2

1

R2D11

2

1R4F7

2

1

R2T1

2

1R2T2

2

1R2R5

21C2D5

541

23

U2R1

21 R2R6

21C2R12

541

23

U2D1

21 R2D12

21C2E4

21 R2E5

541

23

U2E2

2 1R5C11

2 1R5C12

2

1

R5R1

2

1

R5R2

2

1R5R3

Y29Y30

AA34AA33

AB33AB34

AA29AA30

AC32AC31

AB29AB30

AD34AD33

AD29AD30

AC28AC29

AC33AC34

L34L33

M34M33

N31N32

P29P30

N34N33

R29R30

R34R33

T31T32

T29T30

P33P34

T28AA28

D25

B29A29

T33T34

U30U29

U33U34

V31V32

V29V28

W33W34

W30W29

Y33Y34

AA31AA32

V33V34

J30J29

H31H32

H34H33

K30K29

J31J32

L30L29

K33K34

L32L31

M29M30

J34J33

U4D1

C4R27 C4R33 C4R45 C4T22 C5R18 C4R65 C4R60 C4T13

IC

X02056-010

1 OF 8

FSB_CP_GP0_DATA7_DNFSB_CP_GP0_DATA7_DPFSB_CP_GP0_DATA6_DNFSB_CP_GP0_DATA6_DPFSB_CP_GP0_DATA5_DN

XENON_FABK

402

6.3V10%.1UF

X5R

402

5%1K

CH

1K5%EMPTY402

V_GPUCORE

6.3V

402X5R

10%.1UF

CH4025%1K

5%CH402

1K.1UF

X5R

10%

402

6.3V

402X5R6.3V10%.1UF

10%.1UF

402X5R

6.3V

10%

402

6.3VX5R

.1UF

V_MEM

V_MEM

V_MEM

V_MEM

1K5%CH402

5%1K

CH402

402CH5%1K

402

5%CH

1K

V_MEM

5%CH

402CH5%1K

6.3V

402X5R

10%.1UF

V_GPUCORE

X5R6.3V

.1UF

402

10%

402X5R6.3V10%.1UF

1%

402CH

4.87K

402X5R6.3V10%.1UF

402X5R6.3V10%.1UF

MEM_SCAN_EN_BUFF

FSB_GP_CP0_DATA7_DN

FSB_GP_CP1_CLK_DPFSB_GP_CP1_CLK_DN

FSB_BYPCLK_SEL

FSB_CP_GP0_FLAG_DPFSB_CP_GP0_FLAG_DN

FSB_CP_GP0_DATA0_DPFSB_CP_GP0_DATA0_DNFSB_CP_GP0_DATA1_DP

FSB_GP_CP0_FLAG_DNFSB_GP_CP0_FLAG_DPFSB_GP_CP0_CLK_DNFSB_GP_CP0_CLK_DP

FSB_GP_CP0_DATA2_DPFSB_GP_CP0_DATA2_DNFSB_GP_CP0_DATA3_DP

FSB_CP_GP1_CLK_DP

FSB_CP_GP1_DATA2_DPFSB_CP_GP1_DATA2_DNFSB_CP_GP1_DATA3_DP

FSB_CP_GP1_DATA1_DN

FSB_CP_GP1_FLAG_DN

FSB_CP_GP0_DATA5_DP

FSB_CP_GP0_DATA4_DP

FSB_CP_GP0_DATA2_DNFSB_CP_GP0_DATA2_DPFSB_CP_GP0_DATA1_DN

FSB_CP_GP0_DATA4_DN

FSB_CP_GP0_DATA3_DN

FSB_CP_GP1_DATA4_DNFSB_CP_GP1_DATA4_DPFSB_CP_GP1_DATA3_DN

MEM_SCAN_TOP_EN_BUFF

MEM_SCAN_BOT_EN_BUFF

MEM_SCAN_BOT_EN

GPU_SCAN_BUFF_EN_N

MEM_SCAN_TOP_EN

FSB_GP_CP0_DATA5_DP

FSB_GP_CP0_DATA1_DNFSB_GP_CP0_DATA1_DPFSB_GP_CP0_DATA0_DN

FSB_GP_CP0_DATA5_DN

FSB_GP_CP1_DATA2_DP

FSB_CP_GP0_CLK_DP

FSB_GP_CP0_DATA7_DPFSB_GP_CP0_DATA6_DNFSB_GP_CP0_DATA6_DP

FSB_GP_CP1_DATA7_DN

FSB_BYPCLK_DPFSB_BYPCLK_DN

FSB_IMPED_NCAL

FSB_IMPED_CAL

FSB_GP_CP1_DATA7_DP

FSB_GP_CP1_DATA5_DNFSB_GP_CP1_DATA6_DPFSB_GP_CP1_DATA6_DN

FSB_GP_CP1_DATA1_DN

FSB_GP_CP1_DATA0_DP

FSB_GP_CP1_DATA1_DP

FSB_GP_CP0_DATA4_DN

FSB_GP_CP0_DATA0_DP

FSB_CP_GP0_CLK_DN

FSB_CP_GP0_DATA3_DP

FSB_CP_GP1_CLK_DNFSB_CP_GP1_FLAG_DP

FSB_CP_GP1_DATA0_DPFSB_CP_GP1_DATA0_DNFSB_CP_GP1_DATA1_DP

FSB_CP_GP1_DATA5_DPFSB_CP_GP1_DATA5_DNFSB_CP_GP1_DATA6_DPFSB_CP_GP1_DATA6_DNFSB_CP_GP1_DATA7_DPFSB_CP_GP1_DATA7_DN

FSB_GP_CP0_DATA4_DP

FSB_GP_CP1_DATA0_DN

FSB_GP_CP1_FLAG_DN

FSB_GP_CP1_DATA2_DN

FSB_GP_CP1_DATA4_DPFSB_GP_CP1_DATA4_DN

FSB_GP_CP0_DATA3_DN

FSB_GP_CP1_DATA5_DP

FSB_GP_CP1_DATA3_DNFSB_GP_CP1_DATA3_DP

FSB_GP_CP1_FLAG_DP

MEM_SCAN_EN

EMPTY

X801565-001

EMPTY

X801565-001

1K

402

EMPTY

4025%0CH

5%402 CH

0

X801565-001

4020 5%

CH

5%

402CH

0

PAGEMICROSOFT REV

CONFIDENTIAL

PROJECT NAMEDRAWING

INININ

ININ

ININ

ININ

IN

ININININ

INININININ

ININ

INININ

ININ

IN

OUT

GPU VERSION 57

GP_CP0_DATA2_DPGP_CP0_DATA1_DNGP_CP0_DATA1_DPGP_CP0_DATA0_DN

CP_GP0_FLAG_DN

CP_GP0_DATA0_DP

FSB_BYPCLK_SELFSB_BYPCLK_DNFSB_BYPCLK_DP

CP_GP1_DATA6_DNCP_GP1_DATA7_DPCP_GP1_DATA7_DN

FSB_IMPED_NCAL

GP_CP1_FLAG_DPGP_CP1_FLAG_DN

CP_GP1_DATA3_DP

CP_GP1_FLAG_DPCP_GP1_CLK_DNCP_GP1_CLK_DP

CP_GP0_DATA3_DNCP_GP0_DATA3_DP

CP_GP0_DATA4_DPCP_GP0_DATA4_DNCP_GP0_DATA5_DPCP_GP0_DATA5_DN

CP_GP0_DATA6_DNCP_GP0_DATA7_DPCP_GP0_DATA7_DN

GP_CP0_FLAG_DN

GP_CP0_DATA0_DP

GP_CP0_DATA4_DN

GP_CP0_DATA6_DPGP_CP0_DATA5_DNGP_CP0_DATA5_DP

GP_CP1_CLK_DN

GP_CP1_DATA1_DPGP_CP1_DATA0_DNGP_CP1_DATA0_DP

GP_CP1_DATA1_DN

GP_CP1_DATA4_DPGP_CP1_DATA3_DNGP_CP1_DATA3_DPGP_CP1_DATA2_DNGP_CP1_DATA2_DP

GP_CP1_DATA6_DNGP_CP1_DATA6_DPGP_CP1_DATA5_DNGP_CP1_DATA5_DPGP_CP1_DATA4_DN

GP_CP1_DATA7_DNGP_CP1_DATA7_DP

GP_CP1_CLK_DP

GP_CP0_DATA7_DNGP_CP0_DATA7_DPGP_CP0_DATA6_DN

CP_GP0_DATA2_DNCP_GP0_DATA2_DPCP_GP0_DATA1_DNCP_GP0_DATA1_DP

CP_GP0_DATA6_DP

GP_CP0_FLAG_DPGP_CP0_CLK_DNGP_CP0_CLK_DP

GP_CP0_DATA4_DPGP_CP0_DATA3_DNGP_CP0_DATA3_DPGP_CP0_DATA2_DN

FSB_IMPED_PCAL

CP_GP1_FLAG_DN

CP_GP1_DATA6_DPCP_GP1_DATA5_DNCP_GP1_DATA5_DPCP_GP1_DATA4_DNCP_GP1_DATA4_DPCP_GP1_DATA3_DN

CP_GP1_DATA2_DN

CP_GP1_DATA0_DPCP_GP1_DATA0_DNCP_GP1_DATA1_DPCP_GP1_DATA1_DNCP_GP1_DATA2_DP

CP_GP0_DATA0_DN

CP_GP0_FLAG_DPCP_GP0_CLK_DNCP_GP0_CLK_DP

INININ

IN

OUT

IN

ININ

OUT

OUTOUTOUTOUT

OUTOUT

OUT

OUT

OUTOUT

OUTOUTOUTOUTOUT

OUT

OUT

OUT

OUT

OUT

OUT

OUTOUT

OUT

OUTOUTOUT

OUT

OUT

OUT

OUT

OUTOUT

IN

OUTOUT

OUT

OUT

OUT

IN

IN

IN

OUT

SN74LVC1G125

VCC

GND OE_NIN OUT

SN74LVC1G125

VCC

GND OE_NIN OUT

SN74LVC1G125

VCC

GND OE_NIN OUT

ININININ

ININ

OUT

VIDEO DECOUPLING

GPU, VIDEO + PCIEX + EEPROM + JTAG

[PAGE_TITLE=GPU, VIDEO + PCIEX + EEPROM + JTAG] K713/73XENON_RETAIL

1313

29

33

4646

28

29

333333

28

2929

29

12

33

13

13

13

34 34

13

33

29

13

13

29

20 21 22 23 24 25 26 27

13

13

33

33

29

34 56

13

121212

Wed Aug 24 09:27:07 2005

21 R3C28

21 R4D3

21 R4D4

2

1

R5P3

2

1

R5C10

2

1

R4C7

2

1

R4C6

1FT2P13

1FT2P14

2

1

R2E4

1 DB4D1

2

1

R4D2

2

1

R4D1

2

1

R2D10

2

1

R2E3

2

1

R2E2

2

1

R2D9

21 R4R3

654321

J5C2

R4C3

R5C5

R5C8

2 1R4C5

2 1R4C4

3

8

256

7

41

U4C1 2

1C5C3

2

1

R4F62

1

R2E1

21 R4T1

21 R4R8

21 R5D1

87654321

J2D2

A11

G13G11G12

D12E12

E13

G16E16E15

G17

E14

E11 D14

D15B15A15A14D13B13A13B12

B17A17D16B16A16

A12D11

B14D10C10

B23A23B27A27

B22A22B26A26

A28B28B21

C22C23

A25A24

G10G9AN13AG11

V8AG16

B11

G14G15

U4D1

21 R5D2

C3C2 C4R2 C4R26 C4R1

21C5D1

21C4D3

21C4D2

21C4D1

X02056-010

IC2 OF 12

GPU_SPI_SIGPU_SPI_WP_N

402562

EMPTY

X800552-001

EMPTY

V_1P8

EMPTY

402

CH402

1K5%

EMPTY

1K5%

402

402

GPU_PIX_CLK_1X.1UF

6.3V

PEX_GPU_SB_L0_DN

EMPTY4021%49.9

GPU_CLK_DPGPU_CLK_DN

EMPTY49.9 1%402

1%

ANA_PIX_CLK_2X_DP

GPU_TEMP_P

1%

CH V_GPUPCIE

CH1%

V_MEM

X5R805

20%6.3V

10UF

X5R402 402

PEX_PCAL

1.47K402

V_MEMGPU_TRST

40240.2

GPU_TCLK

PEX_SB_GPU_L1_DPPEX_SB_GPU_L1_DNPEX_SB_GPU_L0_DP

PEX_ICAL

ANA_PIX_CLK_2X_DN

EDRAM_TEMP_PEDRAM_TEMP_N

GPU_TEMP_N

1.5K1%

CH

EMPTY

GP

U_S

CA

N_B

UF

F_E

N_N

PEX_SB_GPU_L0_DN

CH4022K

GPU_SPI_CS_N

GPU_SPI_CLK

GPU_SPI_SO

GPU_TMS

GPU_TRST_ED

GPU_SPI_SO_R

GPU_RST_N GPU_RST_DONE

PEX_GPU_SB_L1_DP_C

PEX_GPU_SB_L0_DP_C

PEX_GPU_SB_L0_DN_C

GPU_SROM_EN_PSRO_OUT

MEM_CALB

GPU_SPI_SI

PEX_GPU_SB_L1_DN_C

PEX_GPU_SB_L0_DP

GPU_VSYNC_OUT

GPU_SPI_CS_N

GPU_SPI_SO

GPU_HSYNC_OUT

MEM_RST

GPU_SPI_CLK

GPU_SPI_WP_N

GPU_SPI_CLK_R

GPU_TDIGPU_TDO

MEM_CALA

5%

402CH

1K1K

CH5%

402

6.3VX5R402

.1UF10%

6.3V10%

X5R

.1UF

1%

X5R402

10%

X5R

.1UF

402

1%

X5R

10%6.3V

.1UF

10

234

65

78910

1211

1413

V_1P8

5%

402CH

10K5%CH402

10K

402CH5%10K

CH

10K

402

5%

1.5K

CH1%

402

TP

V_MEM

CH402

1%1.5K

CH402

402

1%

402CH

1.5K

CH1%

5%CH402

1K

1K402 CH

5%

.1UF10%6.3V

4021K

CH5%

10K 5%402

V_1P8

CH5%10K

V_1P8

402X5R

10%

X5R

.1UF

6.3V

PEX_NCAL

6.3V10%

PEX_GPU_SB_L1_DN

PEX_GPU_SB_L1_DP

402

PIX_DATA<14..0>

40240.2

DBG_LED3

1%CH

1.5K

V_MEM

1.27KCH402

XENON_FABK

GPU_SPI_CS_N_R

.1UF10%6.3V

GPU_SPI_SI

MEM_SCAN_BOT_EN_BUFFMEM_SCAN_TOP_EN_BUFFMEM_SCAN_EN_BUFF

DRAWINGPAGEMICROSOFT REV

CONFIDENTIAL

PROJECT NAME

OUT

OUT

IN

IN

IN

ININ

ININ

IN

ININ

2X4HDR

ININ

GPU VERSION 57

PEX_RX1_DNPEX_RX0_DPPEX_RX0_DN

PEX_RX1_DP

PEX_ICAL

PIX_CLK_IN_DP

ED_THERMD_NED_THERMD_P

NB_THERMD_PNB_THERMD_N

PIX_CLK_IN_DN

PIX_DATA2PIX_DATA3PIX_DATA4PIX_DATA5

PEX_NCALPEX_PCAL

RST_IN_N*

NB_CLK_DN

PIX_DATA8PIX_DATA9

PIX_DATA12PIX_DATA11PIX_DATA10

PIX_DATA7PIX_DATA6

PIX_DATA1PIX_DATA0

VSYNC_OUT

SROM_EN_PSRO_OUTSROM_SI

SROM_SCLKSROM_CS

SROM_SO

MEM_RSTMEM_SCAN_EN

MEM_SCAN_OEN_AMEM_SCAN_OEN_B

PEX_TX0_DN

PIX_CLK_OUT

MEM_CALAMEM_CALB

TCLKTDOTDI

TRST_EDTRSTTMS

RST_DONE

PEX_TX1_DPPEX_TX1_DNPEX_TX0_DP

PIX_DATA14PIX_DATA13

HSYNC_OUT

NB_CLK_DP

OUT

OUTOUT

OUT

OUT

OUT

OUT

OUT

IN

OUT

OUTOUTOUT

FTPFTP

IN

OUTOUT

2X3HDR

IN

IN

INAT25020A

GND

SDO

VCC

WP_N*CS_N*HOLD_N*

SDISCK

OUT

OUT

OUTOUTOUT

OUT

MEMORY CONTROLLER B, DECOUPLING

MEMORY CONTROLLER A, DECOUPLING

[PAGE_TITLE=GPU, MEMORY CONTROLLER A + B]

GPU, MEMORY CONTROLLER 0 PARTITION A & B

K714/73XENON_RETAIL

22232223

20212021

2021

2021

2021202120212021

20 21

20212021

2021

20212021

20212021

2021

20212021

2021

2021

20212021

20212021

20212021

20212021

20212021

20212021

2021

202120212021

212120

20 2120 21

21

20 21

20212021

20212021

20212021

2021

2021

22232223

2223

22232223

2223

22232223

2223

2223

22232223

2223

22232223

22232223

2223

22232223

22232223

22232223222322232223

22232223

2223

22232223222322232223

232222

232223

22 2322 2322 2322 23

2223

222322232223

222322232223

20

20

22 23

22 2320 21

20 21

Wed Aug 24 09:27:08 2005

2

1

R4T3

2

1C4T40

2

1

R4T4

2

1 C4T45

AJ9

AP20

AP14

AK19

AM12

AK6AP13

AM18

AL15

AK17

AJ14

AK7

AJ18AH18

AK15AH11AH15AK11

AP19AN19

AH13

AL18AN20AN18AM20AN17AL20

AP15AN15AM15AN14

AK12

AN16AL13AP17AM13

AH16AK20AK16AH20AH17AJ19

AJ13AH12

AP18

AP16

AM17

AK14

AK9AL10

AH10AK10AN12AP12

AN6

AK8

AP10AM10AP5

AP8AN11AP9AN10AP11AN9AN8AN7

AN4AP7AP4

AN5AP6

U4D1

2

1R4T6

2

1

R4T7

C4T35

C4R3

C4T27 C4T41

C4T29 C4T32

C4T43

C4T42 C4T442

1R5E1

2

1 C5E1

2

1

R5E2

2

1 C4T46

2

1

R4T8

2

1R4T5

AF33

AP30

AN22

AK30

AM22

AG33AP21

AN26

AP24

AN28

AJ24

AF31

AK28AK29

AK25AH21AH25AK21

AN27AP28

AH23

AP27AP29AL25AP31AM25AP32

AM23AP23AL23AN23

AK22

AN25AP22AP25AN21

AH26AN32AK26AN31AN29AN30

AJ23AH22

AP26

AN24

AK27

AK24

AH34AF34

AM33AM34AL33AL34

AG34

AF32

AH30AH33AG30

AJ30AK33AJ33AK34AM32AJ34AE30AF28

AK32AE29AE34

AE33AF29

U4D1

C4T47

C4T33 C5T3

C4T31

C5T4 C5T1

C4T34 C5T2 C4T39

X02056-010

IC4 OF 8

X02056-010

IC3 OF 8

MB_DQ1MB_DQ0

XENON_FABK

MA_DQ17MA_DQ16MA_WDQS2

.22UF

6.3V

.22UF

402

10%6.3VX5R

.22UF10%6.3VX5R402

.22UF10%6.3VX5R402

.22UF10%6.3VX5R402

.22UF10%6.3VX5R402

10%

X5R402

.22UF10%6.3VX5R402

.22UF10%6.3VX5R402

6.3V

V_MEM

549

MA_DQ29

.22UF10%6.3VX5R402

.22UF

X5R402

6.3V10%

.22UF

6.3V

402X5R

10%.22UF

6.3VX5R402

10%.22UF

6.3VX5R402

10%

.22UF

402

10%6.3VX5R

.22UF

6.3V10%

X5R402

.22UF

X5R

10%6.3V

402

V_MEM

MA_DQ10MA_DQ11MA_DQ12MA_DQ13

MB_VREF1

MA_RAS_N

MB_VREF0

MA_RDQS0MA_DM0

MA_WDQS0

MA_DQ1MA_DQ0

MA_DQ3MA_DQ2

MA_DQ4

MA_DQ6MA_DQ5

MA_DQ7

MA_DM1

MA_WDQS1MA_RDQS1

MA_DQ8MA_DQ9

MA_DQ15MA_DQ14

MA_DM2MA_RDQS2

MA_DQ18MA_DQ19

MA_DQ21MA_DQ20

MA_DQ22

MA_DQ28MA_DQ27MA_DQ26

MA_CLK1_DPMA_CLK1_DNMA_CLK0_DP

MA_WE_NMA_CAS_N

MA_CS1_N

MA_CKE

MA_DQ25MA_DQ24MA_WDQS3MA_RDQS3

MA_DQ31MA_DQ30

MA_DM3

MA_DQ23

MB_DM0MB_RDQS0MB_WDQS0

MB_DQ3MB_DQ2

MB_DQ4

MB_DQ6MB_DQ5

MB_DQ7

MB_DM1

MB_WDQS1MB_RDQS1

MB_DQ8

MB_DQ10MB_DQ9

MB_DQ12MB_DQ11

MB_DQ13

MB_DQ15MB_DQ14

MB_DM2MB_RDQS2MB_WDQS2MB_DQ16MB_DQ17MB_DQ18MB_DQ19

MB_DQ21MB_DQ20

MB_DQ22

MB_DQ28MB_DQ27MB_DQ26MB_DQ25MB_DQ24

MB_CLK1_DNMB_CLK0_DPMB_CLK0_DN

MB_CLK1_DPMB_DQ23

MB_CKEMB_WE_NMB_CAS_NMB_RAS_N

MB_CS0_NMB_CS1_N

MB_WDQS3MB_RDQS3MB_DM3

MB_DQ31MB_DQ30MB_DQ29

MA_VREF1

MA_CLK0_DN

MA_CS0_N

MA_VREF0

MB_A<12..0>

MB_BA<2..0>MA_BA<2..0>

MA_A<12..0>

1.27K1%

402CH

.1UF10%6.3VX5R402

5491%

402CH

.1UF10%

402X5R6.3V

402CH1%

1.27K1%CH402

V_MEM

V_MEM

1206X5R

10%10UF

012

2

01

345

CH402

1.27K1%

7

X5R6.3V

.1UF

402

10%

1%549

402CH

X5R

.1UF10%6.3V

402

V_MEM

6

98

1110

1.27K

CH402

1%

CH402

5491%

V_MEM

1206

6.3V10%10UF

X5R

12

012

10

234567

98

1110

12

DRAWINGPAGEMICROSOFT REV

CONFIDENTIAL

PROJECT NAME

OUT

OUTIN

BIOUT

BIBIBI

BIBI

BIBI

OUTINOUTBIBIBI

BIBI

OUT

BIBIBI

OUT

OUTIN

BI

BIBI

BIBIBI

GPU VERSION 57

MB_DQ28MB_DQ27MB_DQ26MB_DQ25MB_DQ24

MB_CLK1_DNMB_CLK0_DPMB_CLK0_DN

MB_CLK1_DPMB_DQ23

MB_BA0

MB_CKEMB_WE_N*

MB_CAS_N*MB_RAS_N*

MB_CS0_N*MB_CS1_N*

MB_WDQS1

MB_DQ17MB_DQ18

MB_RDQS1MB_DM1

MB_DQ7MB_DQ6MB_DQ5MB_DQ4

MB_WDQS3MB_RDQS3

MB_DQ22MB_DQ21

MB_DQ19

MB_DQ16MB_WDQS2

MB_DM3

MB_RDQS2MB_DM2

MB_DQ15MB_DQ14MB_DQ13MB_DQ12MB_DQ11MB_DQ10MB_DQ9MB_DQ8

MB_DQ3MB_DQ2MB_DQ1MB_DQ0MB_WDQS0MB_RDQS0MB_DM0

MB_VREF1MB_VREF0

MB_A9MB_A8MB_A7MB_A6MB_A5MB_A4MB_A3MB_A2MB_A1MB_A0

MB_BA2

MB_DQ20

MB_A10MB_A11MB_A12

MB_BA1

MB_DQ31MB_DQ30MB_DQ29

OUTOUTOUT BI

BI

OUTIN

OUT

BIOUT

BIBIBI

BIBI

BIBI

OUTOUT

OUTOUTOUTOUTOUTOUT

OUTOUTOUTOUTOUTOUT

OUT

OUTIN

BIOUT

BIBIBI

BIBI

BIBI

OUTINOUT

BIBIBIBIBIBIBIBI

OUT

OUTIN

BI

BIBI

BIBI

BI

GPU VERSION 57

MA_DQ28MA_DQ27MA_DQ26

MA_CLK1_DPMA_CLK1_DNMA_CLK0_DPMA_CLK0_DN

MA_RDQS2MA_WDQS2

MA_A8MA_A7MA_A6

MA_WE_N*MA_CAS_N*MA_RAS_N*

MA_CS0_N*MA_CS1_N*

MA_CKE

MA_DQ12

MA_DQ25MA_DQ24MA_WDQS3MA_RDQS3

MA_DQ31MA_DQ30MA_DQ29

MA_DQ7MA_DQ6MA_DQ5MA_DQ4MA_DQ3

MA_DM3

MA_DQ23MA_DQ22MA_DQ21MA_DQ20MA_DQ19MA_DQ18MA_DQ17MA_DQ16

MA_DM2

MA_DQ15MA_DQ14MA_DQ13

MA_DQ11MA_DQ10MA_DQ9MA_DQ8MA_WDQS1MA_RDQS1MA_DM1

MA_DQ2MA_DQ1MA_DQ0MA_WDQS0MA_RDQS0MA_DM0

MA_VREF1MA_VREF0

MA_A9

MA_A5MA_A4MA_A3MA_A2MA_A1MA_A0

MA_BA2MA_BA1MA_BA0

MA_A10MA_A11MA_A12

BIBI

OUTIN

BIOUT

BIBIBIBIBIBIBI

OUT

OUT

OUT

MEMORY CONTROLLER D, DECOUPLING

PAGE_TITLE=[GPU, MEMORY CONTROLLER C + D]

MEMORY CONTROLLER C, DECOUPLING

GPU, MEMORY CONTROLLER 1 PARTITION C & D

K715/73XENON_RETAIL

24 25

2627

2627

2425

242524 25

2425

24242525

24

2627

2425

2425

2425

262726 2726 2726 2726 27

2627

25

24 2524 2524 25

2425

2627

262726272627

2425

2425

24252425

2425242524252425

242524252425

24252425

2425242524252425

24252425

24252425

24252425

2425242524252425

2425

2425

24252425

27272626

26272627

26272627262726272627

26272627

26272627

2627

262726272627

2627

2627

26272627262726272627262726272627

2627

2627

262726272627

262726272627

26272627

2627

2425

2425

2425

24252425

2425

26 27

26 2724 25

Wed Aug 24 09:27:10 2005

2

1

R4R5

2

1 C4R25

2

1 C4R10

2

1

R4R2

2

1

R4R1

2

1

R4R4

E7

T1

K1

M7

D2

G1E10

P2

M1

K5

G5

E9

L7M3

H2B2H5C2

R1R3

F2

R2R4N4T2N3U1

L1K4L2K3

E5

N2K2N1J2

J6N6J5N7L5M5

F5E2

P1

M2

K7

G2

E6B3

J1H1F1E1

A8

E8

B4A3B9

B6D1A5A4C1B5A6B7

A10A7B10

A9B8

U4D1

2

1 C4R23

2

1 C4R66

2

1C3R5

2

1C4R38

2

1 C4T12

2

1 C4R32

2

1C4R51

2

1C4T14

2

1C4R48

2

1

R4T2

2

1 C4T36

2

1C4R64

2

1

R4R7

2

1

R4R6

2

1

R3T2

AH1

AD2

V3

AB7

R7

AF1U2

AC2

Y1

Y5

U5

AL1

AA7AB3

V7P6V6P5

AC3AC4

U3

AC1AD1AB1AE2AA2AE1

W2W1Y2V4

R5

Y4V1

AA1V2

W6AC7

W5AC6AA5AB5

T5T7

AB2

Y3

Y7

U7

AH5AG1

AD6AD5AE4AE3

AK1

AJ1

AG5AH2AJ5

AF5AE5AF2AF7AE7AG2AM1AJ2

AK5AL2AM2

AM3AK2

U4D1

2

1C4T7

2

1C4T28

2

1C4R31

2

1C4R12

2

1C4R15

2

1C4R61

2

1C4R19

2

1C4T38

2

1C4R50

X02056-010

IC6 OF 8

X02056-010

IC5 OF 8

2MC_BA<2..0>

MD_DQ23

MD_RDQS3

XENON_FABK

V_MEM

V_MEM

V_MEM

.22UF

6.3V

402

X5R

402

CH

MC_DQ0

MC_DQ4

6.3V

402

.22UF

6.3VX5R402

10%.22UF

402X5R6.3V10%

.22UF

402X5R6.3V10%

.22UF

402X5R6.3V10%

.22UF

402X5R6.3V10%

.22UF

402X5R6.3V10%

.22UF

X5R

10%.22UF

X5R6.3V10%

402

.22UF10%6.3VX5R402

.22UF10%6.3VX5R402

.22UF10%6.3VX5R402

.22UF10%6.3V

402

.22UF

6.3V10%

X5R402

.22UF10%6.3VX5R402

.22UF10%6.3VX5R402

10%

X5R

MC_RAS_NMC_DQ6

MD_VREF1

MC_CLK0_DNMC_CLK0_DPMC_CLK1_DNMC_CLK1_DP

MC_CS0_N

MD_DM0

MC_DQ5

MC_DQ3

MC_DM0

MD_CS0_NMD_CS1_NMD_RAS_NMD_CAS_NMD_WE_NMD_CKE

MD_DM1

MC_CS1_N

MC_CAS_NMC_WE_NMC_CKE

MC_DQ2

MD_WDQS1

MD_DQ2MD_DQ1MD_DQ0

MC_DQ23

MC_DQ20

MC_DQ31MC_DQ30

MC_DQ27MC_DQ26MC_DQ25MC_DQ24MC_WDQS3MC_RDQS3MC_DM3

MC_DQ22MC_DQ21

MC_DQ19MC_DQ18MC_DQ17MC_DQ16MC_WDQS2MC_RDQS2

MC_DQ14MC_DQ13

MC_DQ11MC_DQ10

MC_DQ8MC_WDQS1MC_RDQS1MC_DM1

MC_DQ7

MC_DQ1

MC_WDQS0MC_RDQS0

MD_CLK1_DPMD_CLK1_DNMD_CLK0_DPMD_CLK0_DN

MD_DQ30MD_DQ29

MD_DQ18MD_DQ17MD_DQ16MD_WDQS2MD_RDQS2

MD_WDQS0MD_RDQS0

MD_DQ20MD_DQ19

MD_DQ31

MD_DQ28MD_DQ27MD_DQ26

MD_DM3

MD_DM2

MD_DQ15MD_DQ14MD_DQ13MD_DQ12MD_DQ11MD_DQ10MD_DQ9MD_DQ8

MD_RDQS1

MD_DQ7

MD_DQ5MD_DQ4MD_DQ3

MD_WDQS3MD_DQ24MD_DQ25

MD_DQ22MD_DQ21

MD_DQ6

MC_DQ9

MC_DQ12

MC_DQ15

MC_DQ29MC_DQ28

MC_VREF1

MC_VREF0MD_VREF0

MC_DM2

MD_BA<2..0>

MD_A<12..0>MC_A<12..0>

CH1%

402

1.27K

402

549

CH1%

CH402

1%549

V_MEM

1211

V_MEM

1211

10UF

6.3V10%

X5R1206

V_MEM

10

0

2

12

5

34

7

402

1.27K

CH1%

X5R402

10%.1UF

6.3V

X5R

10%6.3V

.1UF1%

402

1.27K

CH

5491%

402

402CH1%549

6

910

8

1206X5R6.3V10%10UF

10

012

543

76

910

8

CH1%1.27K

402402X5R

10%6.3V

.1UF

402

.1UF10%6.3VX5R

PAGEMICROSOFT REV

CONFIDENTIAL

PROJECT NAMEDRAWING

OUTINOUT

BIBI

OUT

BIBIBIBIBIBI

OUT

OUTIN

BIBIBI

BIBI

BIBIBI

OUTINOUTBIBI

GPU VERSION 57

MD_DQ30MD_DQ29MD_DQ28

MD_CLK1_DPMD_CLK1_DNMD_CLK0_DPMD_CLK0_DN

MD_A12MD_A11MD_A10

MD_CAS_N*MD_RAS_N*

MD_CS0_N*MD_CS1_N*

MD_WE_N*MD_CKE

MD_BA0

MD_A9MD_A8

MD_A3MD_A4

MD_DQ17MD_DQ16MD_WDQS2MD_RDQS2

MD_WDQS0MD_RDQS0MD_DM0

MD_VREF1MD_VREF0

MD_DQ23MD_DQ22

MD_DQ31

MD_DQ27

MD_RDQS3MD_DM3

MD_DM2

MD_DQ15MD_DQ14MD_DQ13MD_DQ12MD_DQ11MD_DQ10MD_DQ9MD_DQ8MD_WDQS1MD_RDQS1MD_DM1

MD_DQ7MD_DQ6MD_DQ5MD_DQ4MD_DQ3MD_DQ2MD_DQ1MD_DQ0

MD_A7MD_A6MD_A5

MD_A2MD_A1MD_A0

MD_BA2MD_BA1

MD_WDQS3MD_DQ24

MD_DQ18MD_DQ19

MD_DQ21MD_DQ20

MD_DQ25MD_DQ26

OUT

OUTOUTOUTOUT

BIBI

BIBI

BIBI

OUTIN

OUT

OUT

BIBI

BIBIBIBIBIBI

OUT

OUT

OUTOUTOUTOUTOUTOUT

OUTOUTOUTOUTOUTOUT

OUT

IN

BIBI

BIBI

OUT

OUT

BI

BIBI

BI

BIBIBI

INOUT

OUT

BIBI

BI

BIBI

IN

BI

OUT

OUT

BI

GPU VERSION 57

MC_DQ30

MC_DQ24MC_WDQS3

MC_CLK1_DPMC_CLK1_DNMC_CLK0_DPMC_CLK0_DN

MC_A9MC_A8MC_A7MC_A6

MC_CAS_N*MC_RAS_N*MC_CS1_N*MC_CS0_N*

MC_WE_N*MC_CKE

MC_A3MC_A2

MC_DQ23

MC_DQ20

MC_DQ29

MC_DQ31

MC_DQ28MC_DQ27

MC_RDQS3MC_DM3

MC_DQ22MC_DQ21

MC_DQ19MC_DQ18MC_DQ17MC_DQ16MC_WDQS2MC_RDQS2MC_DM2

MC_DQ15MC_DQ14MC_DQ13

MC_DQ9MC_DQ8MC_WDQS1MC_RDQS1MC_DM1

MC_DQ7MC_DQ6MC_DQ5MC_DQ4MC_DQ3MC_DQ2MC_DQ1MC_DQ0MC_WDQS0MC_RDQS0MC_DM0

MC_VREF1MC_VREF0

MC_A5MC_A4

MC_A1MC_A0

MC_BA2MC_BA1MC_BA0

MC_A10MC_A11MC_A12

MC_DQ10MC_DQ11MC_DQ12

MC_DQ25MC_DQ26

BIBI

BIBI

BI

IN

BI

OUT

OUT

BIBI

BIBI

BIBIBIBI

OUT

OUT

[PAGE_TITLE=GPU, PLL POWER + FSB POWER]

GPU, PLL POWER + FSB POWER

K716/73XENON_RETAILWed Aug 24 09:27:10 2005

2

1C5R19

2

1C4R68

2

1C4T48

2

1C4D6

2

1 C5R7

2

1 C4R8

21FB4D1

2

1C4D5

2

1C4D4

21FB5R1

2

1C5R13

2

1 C4R5

21FB4R1

2

1C4R4

21FB4T1

2

1C4T30

C5R15

C4R7

C4R6

C26

C24

R32T27U28U31V27V30W28

AA27AB28AB32AC27AD28

W32

AD31K28K31L27M28M32N27P28P31R28

Y28Y31

C27

C25

B24

AG9

F34

A19

A21

B25

AG10

G34

A18

A20

U4D1

C4T37

X02056-010

IC8 OF 12

XENON_FABK

V_PVDDA_ED

V_PVDDA_FSB

V_PVDDA

V_PVDDA_MEM

X7R

0.01UF

402

16V10%

402X7R16V

0.01UF10%

6.3VX5R603

10%2.2UF

603X5R6.3V10%2.2UF

10%2.2UF

6.3VX5R603

X5R

10%2.2UF

603

6.3V

V_GPUPCIE

6.3V

402X5R

.1UF10%

402

.1UF

6.3VX5R

10%

X7R402

0.01UF

16V10%

V_GPUCORE

1200.2A

0.5 DCR

FB603

402

.1UF

6.3VX5R

10%0.01UF

X7R16V10%

402

V_GPUPCIE

V_GPUCORE

1200.2A

0.5 DCR

FB603

402

.1UF

X5R6.3V10%

10%

402

.1UF

6.3VX5R

0.2A0.5 DCR

120 FB603

.1UF

402

6.3VX5R

10%

1200.2A

0.5 DCR

FB603

402

10%

X5R

.1UF

6.3V

0.01UF10%

X7R16V

402

PAGEMICROSOFT REV

CONFIDENTIAL

PROJECT NAMEDRAWING

GPU VERSION 57

VDD_FSB0VDD_FSB1VDD_FSB2VDD_FSB3VDD_FSB4VDD_FSB5VDD_FSB6VDD_FSB7VDD_FSB8VDD_FSB9

VDD_FSB10VDD_FSB11VDD_FSB12VDD_FSB13VDD_FSB14VDD_FSB15VDD_FSB16VDD_FSB17VDD_FSB18VDD_FSB19VDD_FSB20VDD_FSB21VDD_FSB22VDD_FSB23VDD_FSB24

PVSSA_FSBPVDDA_FSB

PVSSA_PEX

PVDDA_MEM

VSS_BSB0VDD_BSB0

PVDDA_PEX

PVSSA_EDPVDDA_ED

PVSSA_MEM

PVDDAPVSSA

VDD_BSB1VSS_BSB1

[PAGE_TITLE=GPU, CORE POWER + MEM POWER]

GPU, CORE POWER + MEM POWER

K717/73XENON_RETAILWed Aug 24 09:27:11 2005

L3L8

L14L15L16L19L20L21L28

M4

Y11

M8M14M15M16M19M20M21M27M31N14

Y12

N15N16N19N20N21N28N29N30

P3P8

Y13

P11P12P13P17

P18P22P23P24P27P32

Y17

R6R11R12R13R17R18R22R23R24R27

Y18

R31T4T8T11T12T13T17T18T22T23

Y22

T24U6U14U15U16U19U20U21U27U32

Y23

V5V14V15V16V19V20V21W4

W8W11

Y24

W12W13W17W18W22W23

F21

W24

F24F26F28F31

G4G7

G18G20G27G29

W27

G33H3H6H8H9

H11H13H15H17H19

W31

H21H23H25H28

J4J8

J28K6

K27K32

Y6

Y27Y32

U4D1

D20D22D30D32D34E17E19E21E31F17

W16

F18F20F23F25F27F29F30G19G28G32

W19H12H14H16H18H20H22H24H26H27J27

W20

L11L12L13L17L18L22L23L24M11M12

W21

M13M17M18M22M23M24N11N12N13N17

Y14

N18N22N23N24P14P15P16P19P20P21

Y15

R14R15R16R19R20R21T14T15T16T19

Y16

T20T21U11U12U13U17U18U22U23U24

Y19

V11V12V13V17V18V22

AA14AA15AA16AA19AA20AA21AB11AB12AB13AB17

V23

AB18AB22AB23AB24AC11AC12AC13AC17AC18AC22

V24

AC23AC24AD11AD12AD13AD17AD18AD22AD23AD24

W14

B18B20C19C21C29C31C33C34D17D18

W15

Y20Y21

U4D1

AF27AF30

AG4AG7

AG13AG15AG17AG20AG23AG25

P4

AG28AG32

AH3AH6AH8AH9

AH14AH19AH24AH27

P7

AH29AH31

AJ4AJ7

AJ11AJ12AJ16AJ21AJ22AJ26

R8

AJ28AJ32

AK3AK13AK23AK31

AL4AL6AL8

AL11

T3

AL14AL17AL21AL24

AL28AL30AL32AM5AM7AM9

T6

AM16AM19AM26AM27AM29AM31AN2AP3C3C5

U4

C7C9C12C14C16C18D4D6D8E3

U8

F4F7F9F11F13F15G3G6G8H4

W3

H7H10J3J7K8L4L6M6

AA4AA6

N5

AB6AC5AC8AD4AD7AE8

AE28AE31

AF3AF6

N8

W7Y8

U4D1

A1AA3AA8

AA11AA12AA13AA17AA18AA22AA23AA24

AB4AB8

AB14AB15AB16AB19AB20AB21AB27AB31AC14AC15AC16AC19AC20AC21AC30

AD3AD8

AD14AD15AD16AD19AD20AD21AD27AD32

AE6AE27AE32

AF4AF8AG3AG6AG8

AG12AG14AG18AG19AG21AG22AG24AG26AG27AG29AG31

AH4AH7

AH28AH32

AJ3AJ6AJ8

AJ10

AJ15AJ17AJ20AJ25AJ27AJ29AJ31AK4AK18AL3AL5AL7AL9AL12AL16AL19AL22AL26AL27AL29AL31AM4AM6AM8AM11AM14AM21AM24AM28AM30AN3AN33B19B33C4C6C8C11C13C15C17C20C28C32D3D5D7D9D19D21D31E4E18E20E22E30E32F3F6F8F10F12F14F16F19

U4D1

X02056-010

IC12 OF 12

BGAX02056-010

IC11 OF 12

BGA

X02056-010

IC10 OF 12

BGA

X02056-010

IC9 OF 12

BGA

XENON_FABK

V_GPUCOREV_GPUCORE

V_MEMV_MEM

PAGEMICROSOFT REV

CONFIDENTIAL

PROJECT NAMEDRAWING

GPU VERSION 51

VSS65

VSS59VSS60

VSS53VSS54VSS55

VSS48VSS49

VSS52VSS51VSS50

VSS43